A revolução do CXL e o fim da memória presa ao soquete da CPU

Esqueça o marketing de 'memória infinita'. Analisamos a realidade técnica do CXL, a transformação do rack em um pool compartilhado e o preço oculto da latência em sistemas desagregados.

Vamos ser honestos: a Lei de Moore está tossindo sangue quando se trata de memória. Enquanto a AMD e a Intel travam uma guerra nuclear para ver quem coloca mais núcleos dentro de um soquete — já passamos de 128 núcleos faz tempo —, ninguém parou para perguntar como vamos alimentar essas bestas.

O resultado? Temos processadores famintos, subutilizados, esperando dados chegarem por canais de memória que simplesmente não escalam na mesma velocidade dos transistores. É aqui que o marketing entra gritando "CXL" como a salvação mágica. Mas, como sempre, a realidade técnica é bem mais suja e cheia de latência do que o PowerPoint sugere.

Resumo em 30 segundos

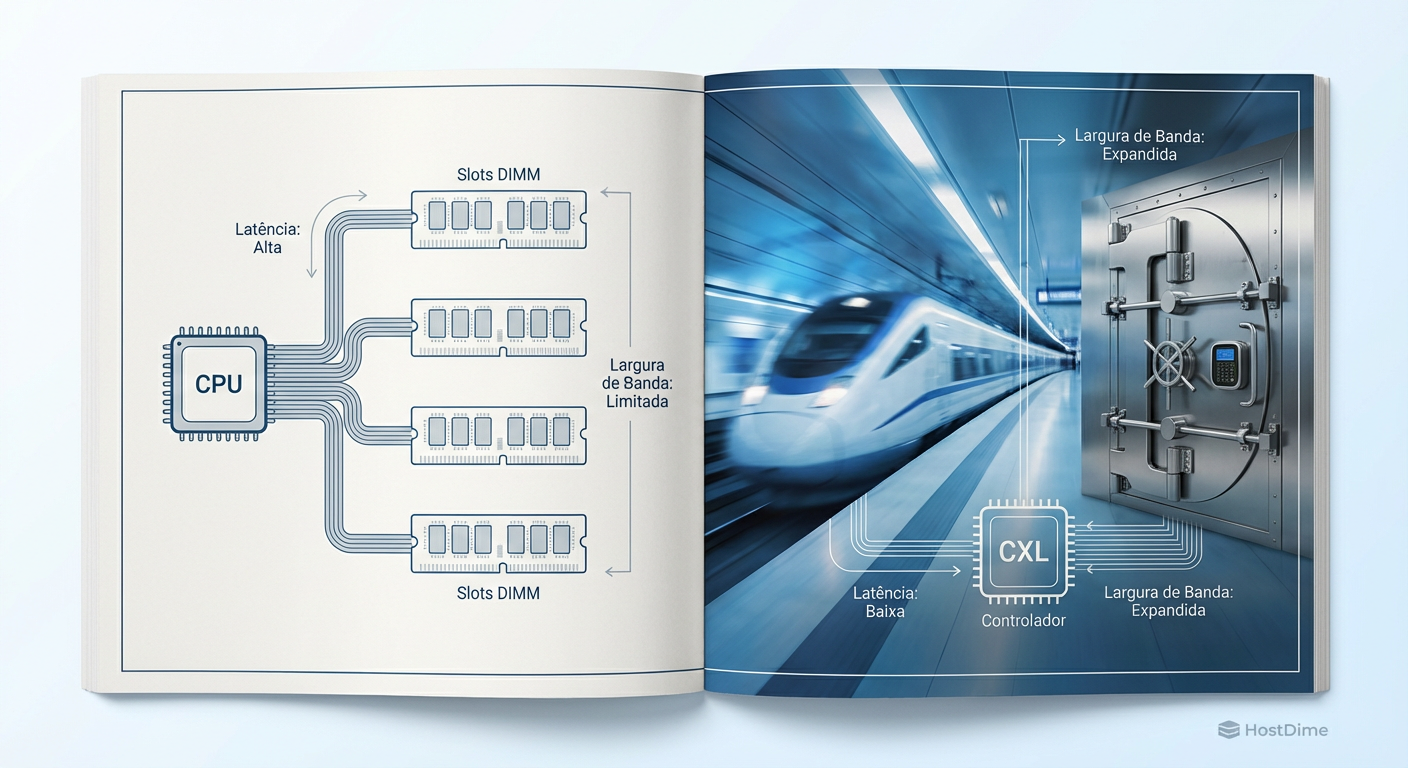

- O Problema: O número de núcleos de CPU cresceu muito mais rápido que a largura de banda da memória, criando um gargalo severo de performance.

- A Solução: O CXL (Compute Express Link) usa o barramento PCIe para conectar memória adicional, permitindo expandir a RAM muito além dos slots DIMM físicos da placa-mãe.

- A Pegadinha: Memória via CXL tem latência maior (semelhante a um nó NUMA distante). Se o seu software não for otimizado para hierarquização (tiering), a performance vai despencar.

O colapso da largura de banda por núcleo

Para entender por que o CXL é inevitável, você precisa olhar para a física da placa-mãe. Adicionar canais de memória DDR5 é um pesadelo de integridade de sinal. Você precisa de mais pinos no soquete da CPU e mais trilhas na PCB. Chegamos a um ponto de ruptura onde simplesmente não cabe mais memória ao redor do processador sem tornar o servidor economicamente inviável ou fisicamente grotesco.

No cenário atual de servidores, estamos vendo a largura de banda por núcleo cair geração após geração. Isso é desastroso para bancos de dados in-memory e aplicações de HPC (High Performance Computing).

É aqui que entra o CXL (Compute Express Link). Em termos simples, o CXL pega a interface física do PCIe (que já é extremamente rápida e onipresente) e roda um protocolo de coerência de cache em cima dela.

Figura: Comparativo arquitetural: A limitação física dos slots DIMM versus a expansão via barramento CXL.

Figura: Comparativo arquitetural: A limitação física dos slots DIMM versus a expansão via barramento CXL.

Desmontando o CXL: Não é apenas "Mais RAM"

O CXL permite conectar dispositivos de memória (Type 3 devices) em slots que parecem PCIe ou em baias de drive (como o formato E1.S ou E3, normalmente usados para NVMe). Para o Sistema Operacional, isso aparece como memória de sistema endereçável. Parece perfeito, certo?

Errado. O marketing esquece de mencionar que a física não perdoa.

Onde a latência mata a performance

A memória conectada diretamente ao controlador de memória da CPU (DDR5 local) tem uma latência extremamente baixa (digamos, ~80-100ns em carga). Quando você move essa memória para o barramento CXL, você está adicionando a sobrecarga do controlador PCIe, a serialização/desserialização e a distância física.

⚠️ Perigo: Testes de campo com implementações CXL 1.1 e 2.0 mostram uma latência adicional de 170ns a 250ns sobre a memória local.

Isso significa que o CXL não é um substituto para a sua RAM principal. Ele é um Tier 2 de memória. Se você tratar memória CXL como memória local para uma carga de trabalho sensível à latência (como logs de transação de alta frequência), seu desempenho vai para o lixo.

A promessa da "Memória Ilhada" (Stranded Memory)

Se a latência é pior, por que os hyperscalers (Google, Meta, Microsoft) estão injetando bilhões nisso? A resposta é TCO (Custo Total de Propriedade).

Em um datacenter tradicional, você compra um servidor com 1TB de RAM. Se sua aplicação usa apenas 200GB, os outros 800GB são "memória ilhada" — paga, energizada, mas inútil. Com o CXL 2.0 e, futuramente, o 3.0, entramos na era do Memory Pooling.

Imagine um chassi cheio de módulos de memória CXL que não pertencem a nenhum servidor específico. Quando o Servidor A precisa de mais RAM para um pico de carga, ele "aluga" 500GB desse pool via barramento. Quando termina, devolve. Isso permite comprar menos memória total para o datacenter, aumentando a utilização de 40-50% para 80-90%.

Tabela Comparativa: DDR5 Local vs. Expansão CXL

| Característica | DDR5 Local (Direct Attach) | Memória CXL (Type 3) |

|---|---|---|

| Latência | Baixa (~80-100ns) | Média/Alta (~200-300ns totais) |

| Largura de Banda | Altíssima (limitada por canais) | Alta (limitada por lanes PCIe 5.0/6.0) |

| Custo por GB | Alto (Premium) | Médio (Commodity + Controller) |

| Capacidade Máxima | Limitada pelos slots da placa-mãe | Teoricamente Petabytes (via Switches) |

| Caso de Uso Ideal | Hot Data, Cache L1/L2 de DBs | Warm Data, In-Memory DB Capacity, AI Models |

O ecossistema de software ainda é uma criança

Aqui está o balde de água fria: o hardware CXL já existe nos processadores modernos (Intel Sapphire/Emerald Rapids, AMD Genoa/Turin), mas o software ainda está engatinhando.

Para que o CXL funcione sem destruir a performance, precisamos de Tiering de Memória Inteligente. O Kernel do Linux e os Hypervisors (VMware vSphere, Nutanix AHV) precisam identificar em tempo real quais páginas de memória são "quentes" (acessadas frequentemente) e mantê-las na DDR5 local, enquanto movem as páginas "mornas" ou "frias" para o CXL.

💡 Dica Pro: Em ambientes Linux, ferramentas como o damon (Data Access MONitor) e políticas de NUMA balancing são críticas. Sem ajuste fino, o sistema pode alocar processos críticos na memória lenta do CXL, causando o que chamamos de "latência de cauda" imprevisível.

O futuro: CXL 3.0 e o fim do servidor como conhecemos

O que estamos vendo hoje com CXL 1.1/2.0 é apenas o começo ponto-a-ponto. A verdadeira revolução — e onde a coisa fica de ficção científica — é o CXL 3.0.

Com a especificação 3.0, introduzimos o conceito de Switched Fabric. Não teremos mais "servidores" com CPU e RAM na mesma caixa de metal fechada. Teremos gavetas de computação (apenas CPUs), gavetas de memória e gavetas de armazenamento, todas conectadas por um switch CXL. O "servidor" será composto via software no momento do boot.

Isso mata o conceito de upgrade físico. Precisa de mais RAM? O software aloca mais do pool do rack. Mas isso exige uma reescrita completa de como pensamos em infraestrutura.

Previsão Técnica

Não corra para implementar CXL em 2026 a menos que você tenha um problema muito específico de capacidade de memória que não pode ser resolvido com DIMMs de 128GB/256GB. A tecnologia é promissora para hyperscalers e provedores de nuvem que precisam otimizar cada centavo de DRAM ociosa.

Para o administrador de storage e infraestrutura "comum", o CXL será invisível por enquanto — virá embutido nas próximas gerações de appliances de armazenamento e servidores de banco de dados como um cache gigante. A revolução é real, mas a latência é a taxa que você paga para entrar nela.

O CXL substitui a memória RAM DDR5 tradicional?

Não. O CXL atua como uma camada de expansão (Tier 2) com maior latência. A memória DDR5 local conectada diretamente ao soquete da CPU continua sendo essencial para dados "quentes" e sensíveis à latência, garantindo que a CPU não fique ociosa esperando dados.Qual é a penalidade de latência ao usar memória via CXL?

Em implementações atuais (CXL 2.0/PCIe 5.0), a latência é comparável a um salto NUMA (aproximadamente 170-250ns adicionais em relação à DRAM local). Isso exige que o sistema operacional ou hypervisor seja inteligente na alocação de dados para evitar degradação de performance.Posso usar módulos CXL em qualquer servidor atual?

Apenas servidores com processadores recentes (como Intel Sapphire Rapids/Emerald Rapids ou AMD EPYC Genoa/Bergamo e superiores) possuem controladores PCIe 5.0 com suporte nativo ao protocolo CXL. Hardware antigo não tem a capacidade de "falar" esse protocolo.O que é "Stranded Memory" e como o CXL resolve isso?

"Memória ilhada" ocorre quando um servidor tem RAM sobrando mas CPU esgotada (ou vice-versa), desperdiçando recursos pagos. O CXL permite "emprestar" essa memória sobrando para outro servidor no mesmo rack (pooling), otimizando drasticamente o TCO do datacenter.

Marcus Duarte

Tradutor de Press Release

"Ignoro buzzwords e promessas de marketing para focar no que realmente importa: especificações técnicas, benchmarks reais e as letras miúdas que os fabricantes tentam esconder."