CXL 3.0: A morte do servidor tradicional e o nascimento da memória líquida

O fim da placa-mãe como conhecemos. Descubra como o CXL 3.0 e o PCIe 6.0 estão transformando datacenters em pools de memória compartilhada e eliminando o gargalo da 'Stranded Memory'.

Estamos testemunhando o funeral silencioso da placa-mãe como a conhecemos. Durante quarenta anos, a arquitetura de servidores obedeceu a uma lei física imutável e cruel: a memória RAM precisa estar fisicamente soldada ou encaixada a poucos centímetros da CPU. Essa tirania da proximidade criou o maior desperdício de capital na história dos datacenters modernos.

O modelo atual de computação é feudal. Cada processador é um senhor feudal que guarda ciosamente seus recursos de memória. Se um servidor está ocioso, seus 512GB de RAM não podem ser "emprestados" para o servidor vizinho que está sufocando em uma carga de trabalho de Inteligência Artificial. Isso acaba agora. Com a chegada do CXL 3.0 (Compute Express Link), estamos prestes a liquefazer o hardware.

Resumo em 30 segundos

- O Fim do Desperdício: Atualmente, até 50% da memória em datacenters é "ilhada" (stranded), presa em servidores que não a utilizam. O CXL permite compartilhar essa memória.

- A Nova Rodovia: Baseado no PCIe 6.0, o CXL 3.0 dobra a largura de banda e permite criar "tecidos" (fabrics) de memória, onde múltiplos servidores acessam o mesmo pool de RAM simultaneamente.

- Hierarquia Redefinida: A distinção entre RAM e Armazenamento (Storage) está desaparecendo. O CXL cria uma camada intermediária de "Far Memory" que é persistente como disco, mas rápida como memória.

O colapso da arquitetura centrada na CPU

A Lei de Moore desacelerou, mas a demanda por dados explodiu. O gargalo não é mais o processamento, é a movimentação de dados. Na arquitetura atual, a CPU é o centro do universo. Tudo — placas de rede, SSDs NVMe, GPUs — precisa passar pelo processador para conversar com a memória. Isso cria latência e engarrafamentos térmicos insustentáveis.

O conceito de "Memória Ilhada" (Stranded Memory) é o vilão silencioso dos orçamentos de TI. Imagine que você construiu um prédio (servidor) com 100 quartos (RAM), mas só tem 20 moradores (uso de CPU). Os outros 80 quartos ficam vazios, trancados, e você não pode alugá-los para o prédio vizinho que está superlotado.

Estudos de hiperescaladores mostram que a utilização média de DRAM em nuvens públicas raramente passa de 40-50%, enquanto os custos de memória representam mais da metade do valor do servidor. Estamos jogando bilhões de dólares no lixo simplesmente porque não conseguimos desatrelar a memória do processador.

Figura: Comparação visual: À esquerda, a memória presa e subutilizada no modelo atual. À direita, o conceito de memória líquida fluindo via CXL para onde é necessária.

Figura: Comparação visual: À esquerda, a memória presa e subutilizada no modelo atual. À direita, o conceito de memória líquida fluindo via CXL para onde é necessária.

CXL 3.0: A revolução do barramento

O Compute Express Link (CXL) não é apenas um novo cabo; é uma mudança de filosofia. Ele utiliza a interface física do PCIe (Peripheral Component Interconnect Express), mas fala uma língua diferente, focada em coerência de cache.

Enquanto o CXL 1.1 e 2.0 prepararam o terreno, o CXL 3.0 é o verdadeiro divisor de águas. Construído sobre a especificação PCIe 6.0, ele utiliza sinalização PAM4 (Pulse Amplitude Modulation 4-level) para atingir taxas de transferência de 64 GT/s. Mas a velocidade é o de menos. A mágica está na topologia.

Diferenças críticas entre as gerações

Para entender o salto, precisamos olhar para o que muda na prática para a infraestrutura de storage e memória:

| Recurso | CXL 1.1 / 2.0 | CXL 3.0 | Impacto no Datacenter |

|---|---|---|---|

| Base Física | PCIe 5.0 (32 GT/s) | PCIe 6.0 (64 GT/s) | Dobro de largura de banda por linha, essencial para IA. |

| Topologia | Ponto-a-Ponto / Switch Simples | Fabric (Tecido) / Multi-nível | Permite redes complexas de memória, não apenas conexões diretas. |

| Compartilhamento | Particionamento de Memória | Compartilhamento de Memória | Vários hosts podem ler/escrever no mesmo endereço de memória (coerência total). |

| Latência | Similar a NUMA remoto | Otimizada, mas física | Exige novos softwares de tiering para gerenciar "Near" vs "Far" memory. |

💡 Dica Pro: Se você gerencia infraestrutura de virtualização (VMware/Proxmox), comece a estudar o conceito de Tiering de Memória. Em breve, você terá que configurar não apenas o vCPU e vRAM, mas qual tipo de vRAM (Local DDR5 ou Remota CXL) sua VM utilizará.

O nascimento da memória líquida

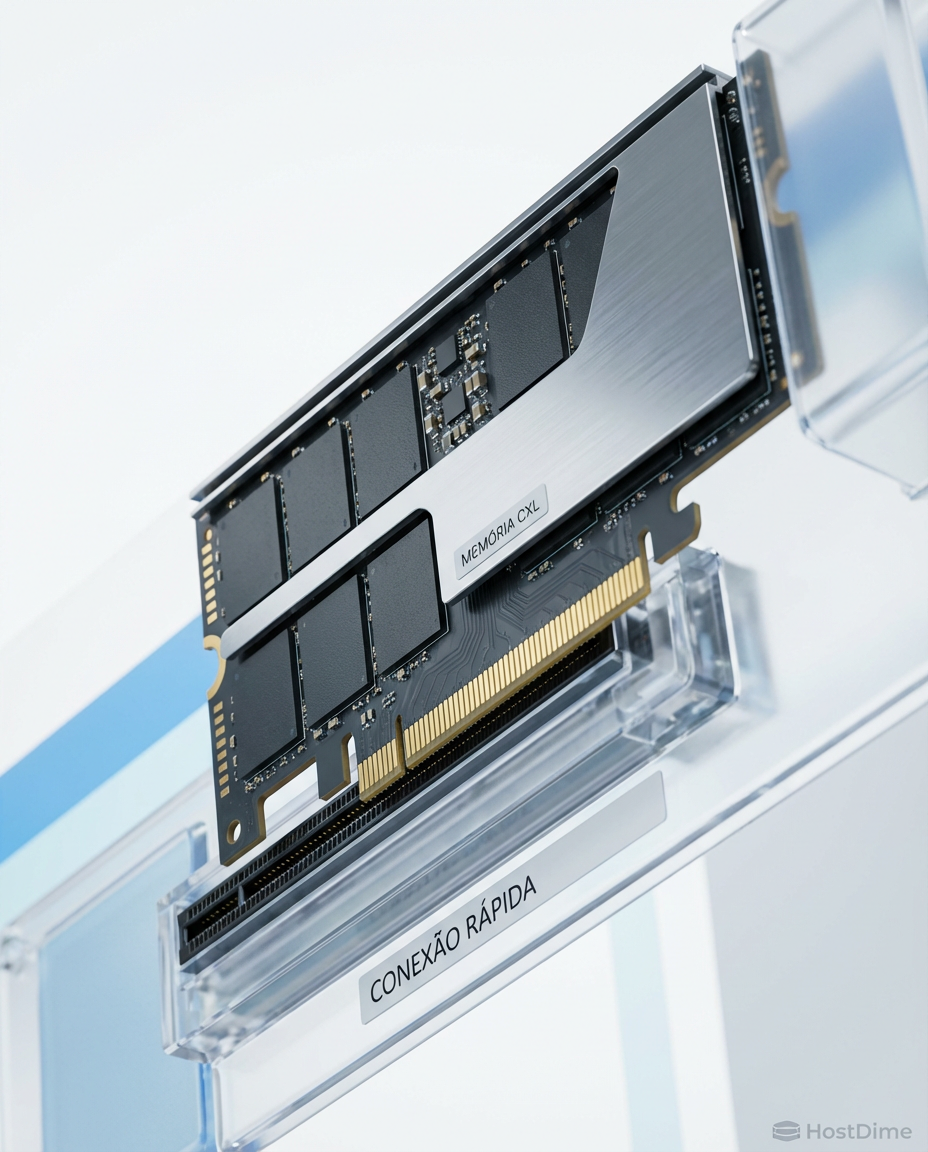

Com o CXL 3.0, a memória deixa de ser um componente estático e se torna um recurso fluido, "líquido". Podemos ter um chassi no rack contendo apenas módulos de memória (seja DRAM DDR5 ou novas tecnologias como SCM - Storage Class Memory) e nenhum processador.

Este chassi, ou "Memory Appliance", conecta-se via cabos PCIe/CXL a múltiplos servidores de computação. Quando um servidor precisa de 1TB de RAM para rodar um banco de dados in-memory (como SAP HANA ou Redis) por duas horas, ele solicita ao tecido CXL. O controlador aloca os endereços. Quando a tarefa termina, a memória volta para o pool e pode ser usada por outro servidor para renderização de vídeo.

A convergência Storage-Memória

Aqui é onde o universo do armazenamento muda para sempre. Até hoje, tínhamos uma linha clara:

Memória (RAM): Rápida, volátil, cara.

Armazenamento (SSD/HDD): Lento, persistente, barato.

O CXL preenche o abismo entre esses dois mundos. Dispositivos CXL Tipo 3 (Expansores de Memória) permitem o uso de mídias que não são tão rápidas quanto a DDR5, mas são muito mais rápidas que um SSD NVMe, e com capacidades de Terabytes.

Isso ressuscita o sonho da Persistência de Memória. Imagine um banco de dados que não precisa carregar dados do SSD para a RAM ao iniciar, porque ele vive em uma memória CXL persistente. O tempo de recuperação de falhas (RTO) cai de minutos para milissegundos.

Figura: A nova pirâmide de hierarquia de dados: O CXL cria uma camada massiva de 'Far Memory' entre a RAM tradicional e os SSDs, acessível por múltiplas CPUs.

Figura: A nova pirâmide de hierarquia de dados: O CXL cria uma camada massiva de 'Far Memory' entre a RAM tradicional e os SSDs, acessível por múltiplas CPUs.

Desafios físicos: A latência não perdoa

Nem tudo é perfeito. Ao mover a memória para fora do soquete da CPU, introduzimos a física implacável da distância. A luz leva tempo para viajar pelo cobre ou fibra.

A memória DDR5 conectada diretamente à CPU tem uma latência na casa dos 60-80 nanossegundos. A memória CXL, passando por controladores, retimers e cabos, adiciona cerca de 170-250 nanossegundos (semelhante a acessar memória em um soquete NUMA vizinho).

⚠️ Perigo: Aplicações sensíveis à latência extrema (High Frequency Trading, simulações em tempo real) podem sofrer degradação se o sistema operacional alocar páginas de memória CXL indiscriminadamente.

A solução virá via software. Os hypervisors e sistemas operacionais (Linux Kernel 6.x já está avançando nisso) precisarão ser inteligentes o suficiente para colocar os dados "quentes" na DDR5 local e os dados "mornos" na memória CXL. É o mesmo princípio do Tiering de Storage que fazemos com SSD e HDD há anos, mas agora aplicado à memória volátil.

O futuro da infraestrutura (2026-2030)

Nos próximos cinco anos, o servidor "caixa de pizza" padrão de 1U ou 2U deixará de ser a unidade atômica do datacenter. A unidade será o Rack.

Veremos a ascensão da Infraestrutura Componível (Composable Infrastructure) real.

Gavetas de Computação: Apenas CPUs e resfriamento.

Gavetas de Memória: Pools de CXL (DRAM + SCM).

Gavetas de Aceleração: GPUs e FPGAs.

Gavetas de Storage: NVMe-oF e JBOFs.

Tudo interligado por um backbone óptico ou de cobre de alta velocidade rodando protocolos CXL. O software definirá o hardware. Você precisa de uma máquina com 4 CPUs e 10TB de RAM hoje? Um comando de API monta esse "servidor virtual" fisicamente disperso no rack, mas logicamente unificado.

Para os profissionais de storage, isso significa que a competência em protocolos de rede e entendimento de latência será mais valiosa do que saber configurar um RAID. O disco virou memória, e a memória virou rede.

O imperativo da adaptação

A transição para o CXL 3.0 não é uma atualização incremental; é uma ruptura arquitetônica. Quem continuar desenhando datacenters baseados na contagem de slots DIMM por servidor estará comprando ativos obsoletos antes mesmo de ligá-los na tomada.

A eficiência energética e o custo total de propriedade (TCO) forçarão essa mudança. Não faz sentido econômico manter silício energizado e ocioso. A memória líquida é a resposta para a sustentabilidade e a escala da próxima era da computação. Preparem seus racks.

Perguntas Frequentes (FAQ)

O que é CXL 3.0 e como ele difere do CXL 2.0?

Enquanto o CXL 2.0 introduziu o pooling de memória (vários hosts acessando um pool de forma particionada), o CXL 3.0, baseado na velocidade do PCIe 6.0, introduz a capacidade de 'Fabric'. Isso permite comutação multinível complexa e o compartilhamento real de memória (coerência de cache) entre CPUs e aceleradores sem passar pelo processador host, dobrando a largura de banda para 64 GT/s.O CXL vai substituir a memória RAM DDR5 tradicional?

Não imediatamente. O CXL atuará como uma camada de memória "Far Memory" (levemente mais lenta, mas com capacidade massiva e compartilhável), enquanto a DDR5 continuará sendo a "Near Memory" soldada ao lado da CPU para tarefas de latência crítica. O futuro é um sistema híbrido e hierárquico onde o software gerencia onde os dados residem.O que é "Stranded Memory" e como o CXL resolve isso?

"Stranded Memory" (memória ilhada) é o fenômeno onde um servidor tem sobra de RAM mas falta de CPU, tornando essa memória inutilizável por outros servidores no mesmo rack. O CXL permite que essa memória excedente seja "emprestada" via barramento para outras máquinas, otimizando drasticamente o TCO (Custo Total de Propriedade) do datacenter.Quais hardwares atuais suportam CXL?

O ecossistema está amadurecendo rapidamente. Processadores como Intel Sapphire Rapids (Xeon de 4ª Geração), Emerald Rapids e AMD EPYC Genoa (Zen 4) já suportam CXL 1.1/2.0. Módulos de memória CXL (como o Samsung CMM-D) e controladores de empresas como Astera Labs e Marvell estão em validação e produção. O suporte total ao CXL 3.0 é esperado nas gerações de hardware enterprise lançadas a partir de 2026.

Julian Vance

Futurista de Tecnologia

"Exploro as fronteiras da infraestrutura, do armazenamento em DNA à computação quântica. Ajudo líderes a decodificar o horizonte tecnológico e construir o datacenter de 2035 hoje."