CXL 3.1 e a Nova Era da Memória Desagregada em Servidores de IA

Análise estratégica sobre como o CXL 3.1 está eliminando o gargalo de memória em datacenters de IA, transformando RAM em um recurso de rede e reduzindo o TCO.

O mercado de infraestrutura de dados enfrenta um paradoxo silencioso, mas financeiramente devastador. Enquanto os investimentos em GPUs para Inteligência Artificial (IA) dominam as manchetes e os orçamentos de CAPEX, um gargalo menos glamoroso ameaça estrangular a eficiência desses clusters: a capacidade de memória do sistema. A arquitetura tradicional de servidores, onde a DRAM está fisicamente presa e limitada aos slots da placa-mãe (DIMMs) adjacentes à CPU, atingiu seu limite físico e econômico.

Estamos observando uma mudança tectônica na forma como os datacenters são desenhados. A introdução do CXL (Compute Express Link), especificamente em sua iteração 3.1, não é apenas uma atualização de protocolo; é a fundação para a desagregação total da memória. Para analistas de infraestrutura e CIOs, entender essa transição é vital para não investir em hardware que se tornará obsoleto antes mesmo da depreciação contábil.

Resumo em 30 segundos

- O Problema: A quantidade de núcleos de CPU e a demanda de dados de IA crescem muito mais rápido que a capacidade de memória DDR5 por soquete, criando "memória encalhada" e subutilização de recursos.

- A Solução CXL 3.1: Baseado no PCIe 6.0, este protocolo permite que a memória RAM seja compartilhada via "fabric" entre vários servidores, dobrando a largura de banda e permitindo comunicação ponto a ponto sem intervenção da CPU.

- Impacto no Mercado: A desagregação promete reduzir o TCO (Custo Total de Propriedade) em até 30% ao eliminar o superprovisionamento de DRAM, criando uma nova camada de memória entre a RAM direta e o armazenamento NVMe.

O colapso da arquitetura de memória direta

Historicamente, a relação entre CPU e memória sempre foi monogâmica e rígida. Você compra um servidor com dois processadores e preenche os slots DIMM. Se sua aplicação precisa de mais memória do que os slots permitem, você é forçado a comprar outro servidor completo (CPU, placa-mãe, rede, energia), mesmo que não precise de mais poder de processamento.

No cenário atual de Large Language Models (LLMs) e bancos de dados in-memory massivos (como SAP HANA ou Redis em escala), essa rigidez é insustentável. Os modelos de IA exigem terabytes de dados acessíveis em latência de nanossegundos. A memória HBM (High Bandwidth Memory) nas GPUs é rápida, mas proibitivamente cara e escassa em capacidade. A DRAM DDR5 é a alternativa, mas a densidade física dos módulos não acompanha a Lei de Moore necessária para os dados.

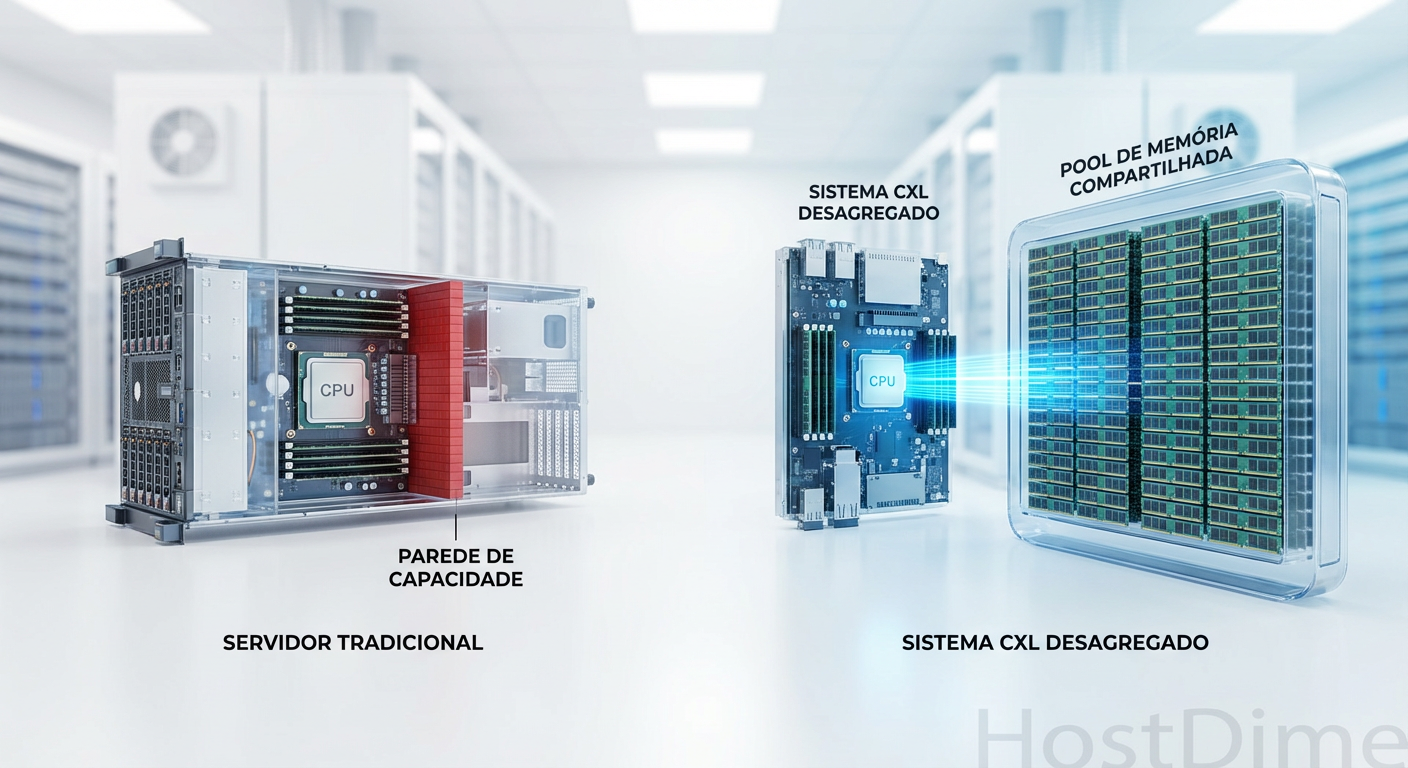

O resultado é o que chamamos de "Memory Wall" (Muro da Memória). Os processadores modernos, como os AMD EPYC Genoa ou Intel Xeon Sapphire Rapids, possuem núcleos suficientes para processar cargas imensas, mas passam ciclos ociosos esperando dados que não cabem na memória local.

Figura: Comparativo visual: A rigidez da arquitetura tradicional versus a flexibilidade do pool de memória via CXL.

Figura: Comparativo visual: A rigidez da arquitetura tradicional versus a flexibilidade do pool de memória via CXL.

CXL 3.1: Transformando RAM em recurso de rede

O Compute Express Link (CXL) é um padrão aberto de interconexão de alta velocidade. Enquanto as versões 1.1 e 2.0 focavam na expansão de memória atrás de um único host ou pooling simples, o CXL 3.1 introduz capacidades reais de fabric. Baseado na camada física do PCIe 6.0, ele dobra a taxa de transferência para 64 GT/s em comparação ao CXL 2.0.

A grande inovação estratégica do 3.1 é a capacidade de suportar topologias de rede complexas. A memória não é mais "de um servidor"; ela é um recurso no rack que pode ser alocado dinamicamente.

Diferenciais Técnicos do CXL 3.1

Peer-to-Peer (P2P): Periféricos podem conversar entre si sem passar pela memória do host. Uma GPU pode acessar um pool de memória CXL diretamente. Isso reduz a latência e libera a CPU de tarefas de movimentação de dados.

Compartilhamento de Memória Global: Múltiplos hosts podem acessar o mesmo endereço de memória simultaneamente (com coerência de cache gerenciada), essencial para clusters de computação de alto desempenho (HPC).

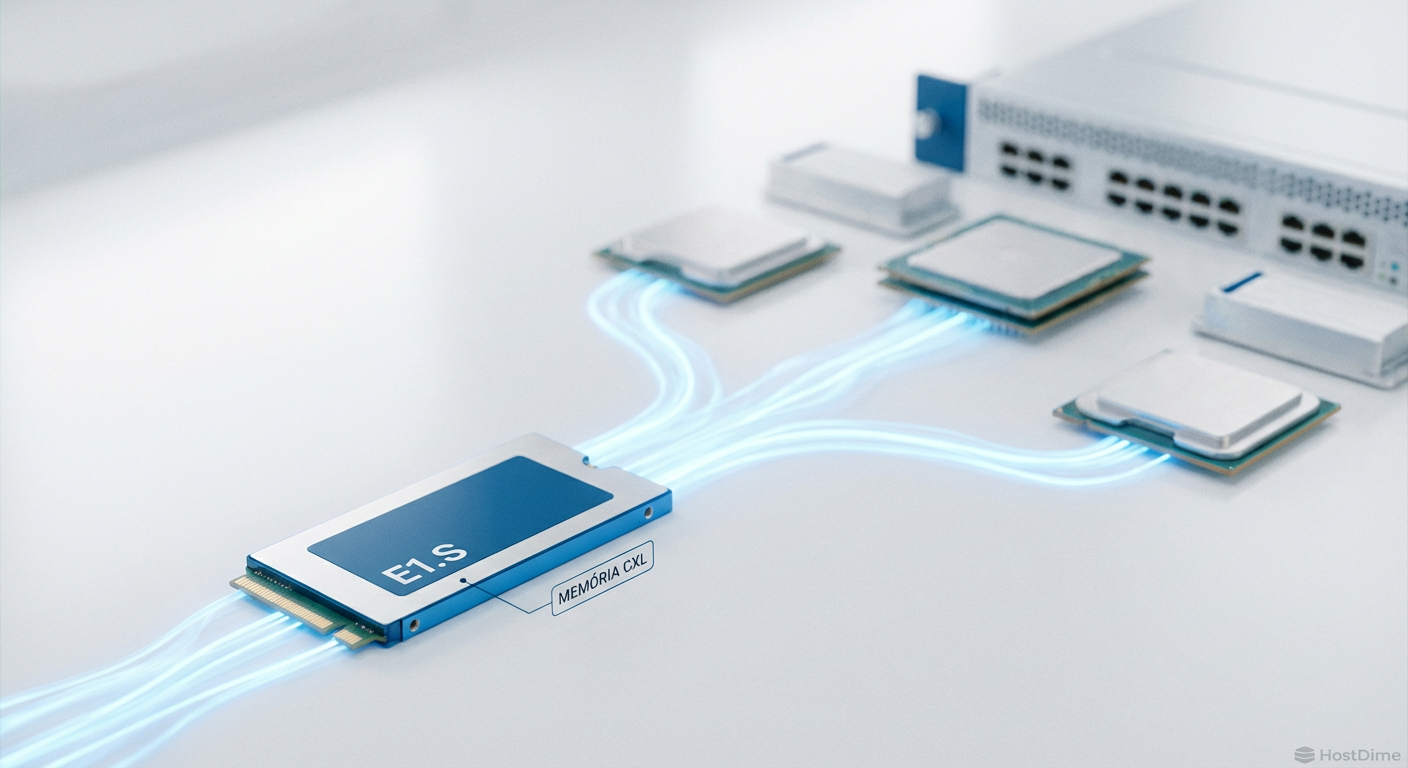

Form Factors Novos: O mercado está adotando o padrão EDSFF (Enterprise & Data Center SSD Form Factor), especificamente o E1.S e E3, para módulos de memória CXL. Isso significa que a "RAM" do futuro parecerá fisicamente com um SSD NVMe, inserida em baias frontais do servidor para fácil manutenção.

💡 Dica Pro: Ao avaliar novos servidores para 2025/2026, verifique o suporte a PCIe 6.0 e CXL 2.0/3.0 na placa-mãe. Sem isso, você estará preso à arquitetura legada de memória direta, perdendo a capacidade de expansão futura.

Tabela Comparativa: Evolução do Acesso à Memória

| Característica | DDR5 Direta (Padrão Atual) | CXL 2.0 (Expansão/Pooling) | CXL 3.1 (Fabric/Desagregado) |

|---|---|---|---|

| Latência | Baixíssima (~70-100ns) | Média (~170-250ns) | Média (~170-250ns) |

| Largura de Banda | Limitada pelos canais da CPU | 32 GT/s (PCIe 5.0) | 64 GT/s (PCIe 6.0) |

| Escalabilidade | Limitada aos slots físicos | Expansão local ou pool simples | Escala de Rack/Fabric |

| Acesso GPU | Via CPU Host | Via CPU Host | Direto (Peer-to-Peer) |

| Custo por GB | Alto (DRAM Premium) | Médio (DRAM Commodity) | Médio (Otimizado por uso) |

A economia oculta: O fim da "Memória Encalhada"

Para o CFO e o analista de mercado, o argumento técnico do CXL é secundário ao argumento financeiro. O conceito de "Stranded Memory" (Memória Encalhada) é o vilão oculto do TCO em datacenters.

Imagine um cluster de 1000 servidores. Para garantir performance, a TI superprovisiona cada servidor com 512GB de RAM. No entanto, a média de uso real pode ser de apenas 300GB. Os 212GB restantes em cada servidor estão "presos". Eles foram pagos, consomem energia (refresh de DRAM), ocupam espaço, mas não podem ser usados por outro servidor que esteja sofrendo com falta de memória.

Com o CXL, a arquitetura muda para um modelo Composable (Componível). Os servidores podem ter apenas a memória mínima necessária para o boot e o sistema operacional (ex: 64GB), enquanto o restante da capacidade é alocado sob demanda a partir de um pool compartilhado via CXL.

Estudos de mercado indicam que a adoção de pools de memória CXL pode reduzir a necessidade de compra de DRAM global em um datacenter em 20% a 30%. Considerando que a memória representa frequentemente 40-50% do custo de um servidor de IA, a economia é multimilionária. Empresas como Astera Labs, Samsung e SK Hynix já estão posicionando seus módulos CXL como a chave para essa eficiência.

Figura: O fim do desperdício: Visualizando como o pooling de memória elimina a capacidade ociosa presa em servidores individuais.

Figura: O fim do desperdício: Visualizando como o pooling de memória elimina a capacidade ociosa presa em servidores individuais.

O "imposto" da latência e a realidade técnica

Apesar do otimismo, é crucial manter uma visão sóbria. O CXL não substitui a memória DDR5 principal, nem a HBM das GPUs. Existe um "imposto" físico inevitável: a latência.

Adicionar controladores, switches e cabos entre a CPU e a memória adiciona nanossegundos preciosos ao tempo de acesso. Enquanto a memória local responde em cerca de 80ns, a memória CXL pode levar entre 170ns a 250ns (semelhante a um acesso NUMA de outro soquete).

Portanto, a estratégia de implementação deve ser baseada em Tiering de Memória (Hierarquização):

Tier 0 (HBM): Dados críticos de treinamento de IA e kernels de computação.

Tier 1 (DDR5 Local): Sistema operacional, metadados quentes e caches L1/L2.

Tier 2 (CXL Memory): Grandes datasets de inferência, bancos de dados in-memory, cache de aplicações.

Tier 3 (NVMe SSD): Armazenamento persistente de alta performance.

O software de gerenciamento (Hypervisors como VMware vSphere ou orquestradores Kubernetes) terá o papel vital de mover dados "mornos" e "frios" da DDR5 cara para o CXL, de forma transparente para a aplicação.

⚠️ Perigo: Implementar CXL sem uma estratégia de software definida (Tiering) pode degradar a performance. Aplicações sensíveis à latência não devem rodar exclusivamente em memória CXL sem otimização prévia.

Perspectivas para a infraestrutura Composable

A transição para o CXL 3.1 marca o início real da Infraestrutura Composable. Nos próximos trimestres, veremos o lançamento de chassis de memória dedicados (Memory Appliances) que se conectam aos servidores via cabos PCIe/CXL.

Isso altera a dinâmica de fornecedores. Fabricantes de storage tradicionais (como Dell, HPE, NetApp) e novos players de semicondutores (Marvell, Microchip) estão correndo para dominar o mercado de controladores CXL. A batalha não será apenas por quem vende o disco ou a memória, mas por quem controla o "fabric" que conecta tudo isso.

Para o mercado de storage, a linha entre "Memória" e "Armazenamento" ficará cada vez mais tênue. Dispositivos CXL podem conter memória persistente ou flash NAND de baixíssima latência, atuando como um híbrido que desafia as categorias tradicionais da IDC.

O Caminho à Frente

A adoção do CXL 3.1 não é uma questão de "se", mas de "quando". O ciclo de renovação de hardware de 2025 e 2026 será fortemente pautado por essa tecnologia, impulsionado pela necessidade insaciável da IA Generativa por memória. Organizações que planejam suas infraestruturas hoje ignorando a desagregação de memória correm o risco de construir datacenters ineficientes e com custos operacionais inflados. A recomendação estratégica é iniciar provas de conceito (PoC) com hardware compatível com CXL 2.0 agora, preparando o terreno lógico e de software para a chegada massiva do CXL 3.1 e do PCIe 6.0.

O que diferencia o CXL 3.1 das versões anteriores (1.1 e 2.0)?

Enquanto o CXL 2.0 introduziu o pooling básico, o CXL 3.1 (baseado em PCIe 6.0) dobra a largura de banda para 64 GT/s e permite arquiteturas de 'fabric' complexas, onde a memória pode ser acessada ponto-a-ponto (P2P) sem passar pela CPU host, essencial para clusters de IA.O CXL vai substituir a memória HBM nas GPUs?

Não. A HBM (High Bandwidth Memory) continua sendo insuperável em velocidade para treinamento imediato. O CXL atua na camada de capacidade e expansão, oferecendo terabytes de memória 'perto o suficiente' para inferência e grandes datasets, a um custo muito menor que a HBM.Qual o impacto do CXL no custo total de propriedade (TCO)?

O CXL permite reduzir drasticamente a 'memória encalhada' (stranded memory). Em vez de superprovisionar cada servidor com RAM que fica ociosa, os datacenters podem criar um pool compartilhado, reduzindo a necessidade de compra de DRAM em até 20-30%.

Arthur Siqueira

Analista de Mercado de Storage

"Analiso o cenário macroeconômico do armazenamento corporativo. Meu foco está nos movimentos de consolidação, flutuações de market share e na saúde financeira que dita o futuro dos grandes players."