CXL e IA: A desagregação de memória não é mágica, é engenharia de compromissos

Análise técnica sobre como o Compute Express Link (CXL) resolve o gargalo de memória em cargas de IA, os custos reais de latência (ns) e o estado atual do hardware.

Vamos ser brutalmente honestos por um minuto. Se você tem acompanhado as conferências de infraestrutura de TI ou lido os whitepapers brilhantes da Intel, AMD e Samsung, provavelmente acredita que o CXL (Compute Express Link) é a varinha mágica que resolverá todos os gargalos de IA do mundo. O discurso de vendas é sedutor: "Adicione memória infinita ao seu servidor via PCIe e esqueça os limites da DRAM".

A realidade, como sempre, é muito mais suja e cheia de nuances técnicas que os slides de marketing convenientemente ignoram. O CXL não é uma revolução mágica de desempenho; é uma ferramenta de sobrevivência econômica e arquitetural para um mundo onde a CPU e a GPU ficaram rápidas demais para a memória que as alimenta.

Resumo em 30 segundos

- Não é DDR5 Local: O CXL permite expandir a memória RAM via slots PCIe, mas introduz uma latência adicional significativa (cerca de 170ns ou mais).

- O Fator Custo: A tecnologia visa resolver o custo proibitivo de super-provisionar servidores com DDR5 ou HBM apenas para atingir capacidades de pico.

- Dependência de Software: Sem um hypervisor ou sistema operacional capaz de fazer tiering inteligente (movendo dados quentes para a RAM local e mornos para o CXL), o desempenho da sua aplicação vai despencar.

O muro de memória e a crise da IA

As arquiteturas atuais de IA atingiram uma parede de concreto armado. Modelos de linguagem grandes (LLMs) como GPT-4 ou Llama 3 não são apenas famintos por computação; eles são devoradores de capacidade de memória. O problema é que a memória mais rápida, a HBM (High Bandwidth Memory) que vive colada na GPU, é astronomicamente cara e limitada em capacidade.

Do outro lado, temos a DRAM DDR5 tradicional. Ela é rápida, mas você está limitado fisicamente pelo número de canais de memória que a CPU suporta. Se você encher todos os slots de um servidor com pentes de 128GB ou 256GB, o custo do servidor explode e a velocidade do barramento de memória muitas vezes cai para manter a estabilidade elétrica.

É aqui que entra o CXL. Em termos simples, o CXL usa a interface física do PCIe 5.0 (e futuramente 6.0) para falar uma linguagem de coerência de cache. Isso permite que você conecte um dispositivo que parece um SSD (fator de forma E1.S ou placa PCIe), mas que o sistema operacional enxerga como memória RAM endereçável.

A penalidade de latência que ninguém menciona

Aqui é onde desmontamos o hype. O marketing diz "expansão de memória". A engenharia diz "NUMA distante".

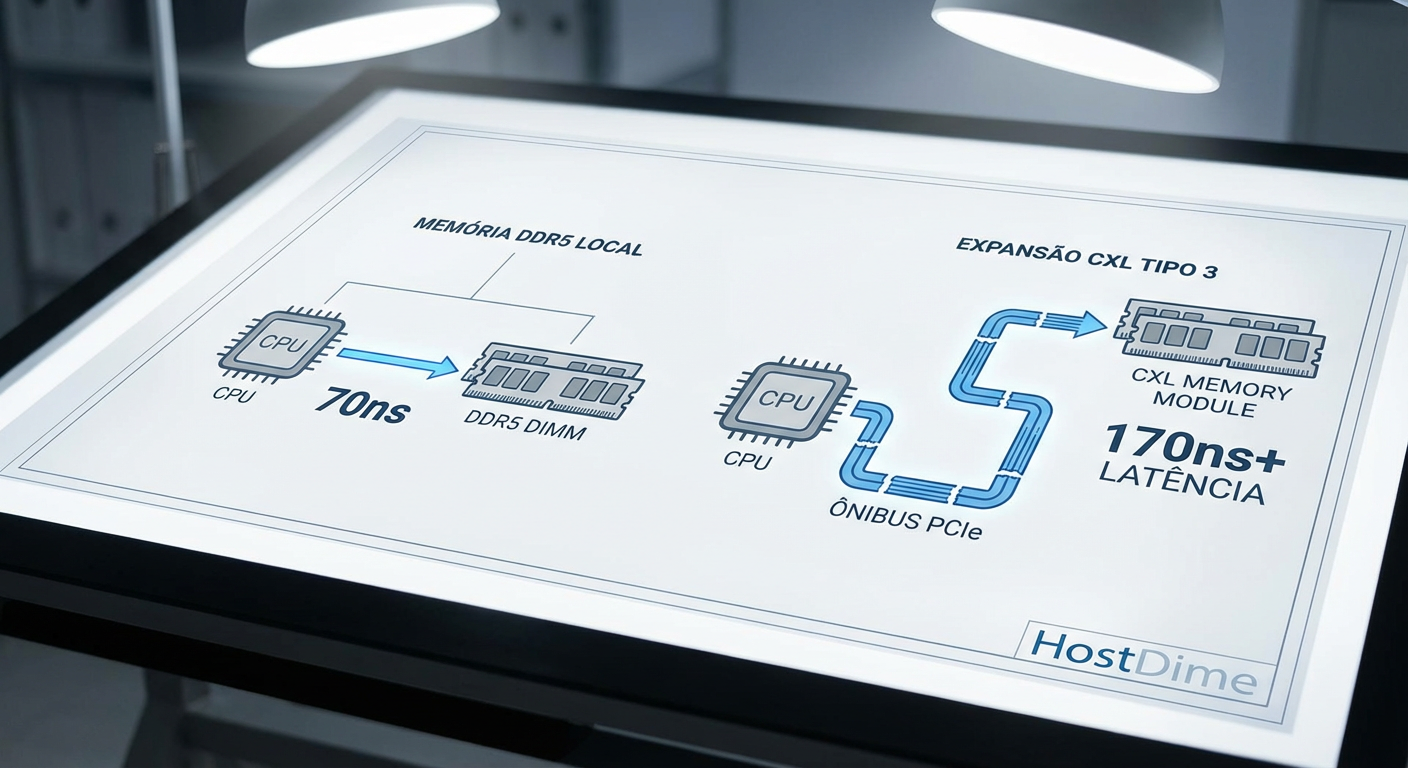

Quando sua CPU acessa a memória DDR5 conectada diretamente ao soquete, a latência gira em torno de 70 a 80 nanosegundos. É instantâneo. Quando você acessa a memória via CXL, você está passando por um controlador CXL, descendo pelo barramento PCIe, entrando no controlador do dispositivo de memória e só então acessando o chip DRAM.

⚠️ Perigo: Testes de engenharia mostram que a latência em implementações CXL 2.0 adiciona cerca de uma "viagem" de NUMA (Non-Uniform Memory Access). Estamos falando de 170ns a 250ns de latência total.

Para um banco de dados transacional de alta frequência, isso é um desastre. Para inferência de IA, onde o throughput (largura de banda) importa mais que a latência de um único acesso, é aceitável. O segredo sujo é que o CXL transforma a RAM em um "tier" intermediário. Não é tão rápido quanto a RAM local, mas é ordens de magnitude mais rápido que um SSD NVMe.

Figura: Comparativo de latência: O caminho direto da DDR5 local versus a rota longa através do protocolo CXL sobre o barramento PCIe.

Figura: Comparativo de latência: O caminho direto da DDR5 local versus a rota longa através do protocolo CXL sobre o barramento PCIe.

O Hypervisor como guarda de trânsito

Se o hardware introduz latência, o software precisa escondê-la. É aqui que a infraestrutura de servidores se torna crítica. Você não pode simplesmente plugar memória CXL e esperar que o Windows ou Linux resolva tudo magicamente sem configuração.

Os hypervisors modernos (como as versões mais recentes do VMware vSphere ou kernels Linux otimizados para datacenter) precisam atuar como gerentes de tiering agressivos. O conceito é similar ao que fazemos em storage há anos com SSDs e HDDs, mas agora na memória volátil:

Tier 0 (DDR5 Local): Dados "quentes", acessados constantemente pela CPU/GPU.

Tier 1 (CXL Memory): Dados "mornos", que não cabem na RAM local mas precisam ser acessados sem a penalidade de ir ao disco.

Tier 2 (NVMe/SSD): Armazenamento frio ou swap.

Se o seu software de orquestração de containers (Kubernetes) ou seu hypervisor não for "CXL-aware", ele pode alocar um processo crítico inteiramente na memória CXL, resultando em uma degradação de performance que fará seu CIO questionar o investimento. A "mágica" depende inteiramente de algoritmos de predição de página que movem dados entre a DDR5 e o CXL antes que a CPU precise deles.

Tabela Comparativa: Onde o CXL se encaixa

Para visualizar onde essa tecnologia se posiciona no ecossistema de armazenamento e memória, veja os dados frios:

| Característica | DDR5 Local (Direct Attach) | CXL Memory (Type 3) | SSD NVMe Enterprise |

|---|---|---|---|

| Latência Típica | ~70-80 ns | ~170-250 ns | ~80.000 ns (80 µs) |

| Largura de Banda | Extrema (Centenas de GB/s) | Alta (Limitada por PCIe x16) | Média/Alta |

| Capacidade por Mod. | Limitada (ex: 64GB-256GB) | Alta (ex: 512GB+) | Massiva (30TB+) |

| Custo por GB | $$$$ | $$$ | $ |

| Persistência | Volátil | Volátil (geralmente) | Persistente |

| Uso Ideal | Kernel, Hot Data, Cache L1/L2 | In-Memory DB, AI Checkpoints | Armazenamento de Dados |

O futuro: CXL 3.0 e a infraestrutura "Composable"

O que temos hoje no mercado é majoritariamente CXL 1.1 e 2.0. Isso significa expansão direta: um servidor, um cabo (ou slot), mais memória. É útil, mas não é transformador.

A verdadeira mudança de jogo, que os fabricantes prometem para os próximos anos com o CXL 3.0, é o "Memory Pooling" e "Switching". Imagine um rack de servidores onde a memória não pertence a nenhuma CPU específica. Existe uma gaveta cheia de módulos de memória CXL conectados a um switch.

Quando o Servidor A precisa treinar um modelo de IA pesado na sexta-feira à noite, o orquestrador atribui 2TB de RAM desse pool para ele. Quando o trabalho termina, essa memória é liberada e reatribuída ao Servidor B para processamento de banco de dados. Isso é a infraestrutura composable (componível).

💡 Dica Pro: Não planeje sua infraestrutura atual baseada em slides de CXL 3.0. A realidade atual (CXL 2.0) é de expansão de capacidade local, não de compartilhamento via fabric. O hardware de switch CXL ainda é embrionário e caro.

O veredito técnico

O CXL é inevitável, não porque é perfeito, mas porque a física e a economia não nos deixam outra escolha. A densidade dos núcleos de CPU está crescendo mais rápido do que a capacidade dos canais de memória. Sem o CXL, teríamos processadores de 128 núcleos famintos, esperando dados chegarem de SSDs lentos.

No entanto, encare o CXL como ele é: uma camada de cache L4 glorificada ou um "SSD ultra-rápido que finge ser RAM". Se você dimensionar sua infraestrutura de IA tratando memória CXL como equivalente exato à DDR5 local, você terá problemas de latência de cauda que arruinarão seus SLAs. Use-o para capacidade, use-o para bancos de dados in-memory gigantescos, mas nunca esqueça a física por trás do conector.

O CXL substitui a memória RAM DDR5 tradicional?

Não. O CXL atua como uma camada de expansão (Tier 2) com maior capacidade, mas latência ligeiramente superior, complementando a DDR5 local. Ele serve para aumentar o volume total de memória disponível sem ocupar os canais principais da CPU.Qual é a latência real de um módulo de memória CXL?

Em implementações atuais (CXL 2.0), a latência gira em torno de 170-250 nanosegundos. Isso é comparável a acessar memória em um soquete de CPU vizinho em um sistema dual-socket (o chamado "NUMA hop"), sendo mais lento que a RAM local (~80ns), mas muito mais rápido que um SSD.O CXL funciona em qualquer servidor?

Não. Exige processadores compatíveis de gerações recentes (como Intel Sapphire Rapids/Emerald Rapids ou AMD Genoa/Bergamo) e suporte específico na placa-mãe e BIOS para habilitar as pistas PCIe como interfaces CXL.

Marcus Duarte

Tradutor de Press Release

"Ignoro buzzwords e promessas de marketing para focar no que realmente importa: especificações técnicas, benchmarks reais e as letras miúdas que os fabricantes tentam esconder."