Diagnóstico de camada física em storage PCIe 5.0: além da troca de peças

Aprenda a diagnosticar falhas de integridade de sinal em NVMe PCIe 5.0. Guia técnico sobre perda de inserção, retimers, cabos MCIO e análise de logs AER.

Diagnóstico de camada física em storage PCIe 5.0: além da troca de peças

Você acabou de provisionar um novo servidor de armazenamento all-flash. O datasheet prometia 14 GB/s por drive em leituras sequenciais. O orçamento foi aprovado, o hardware chegou, os SSDs NVMe Gen5 (seja no formato U.2, E1.S ou E3) foram instalados. Mas, ao rodar o primeiro benchmark sintético com fio, os números não batem. Pior: um dos drives desaparece aleatoriamente ou o dmesg do Linux começa a cuspir erros de AER (Advanced Error Reporting).

O instinto do técnico de suporte padrão é acionar a garantia e trocar o SSD. O mecânico de datacenter experiente sabe que, na era do PCIe 5.0 e seus implacáveis 32 GT/s (Gigatransfers por segundo), o problema raramente é o silício do drive. O problema é a estrada por onde os dados trafegam.

Bem-vindo ao mundo da integridade de sinal, onde um cabo MCIO dobrado incorretamente ou um riser card mal encaixado custam gigabytes de performance.

Resumo em 30 segundos

- Velocidade não é garantida: Se a integridade do sinal cair, o protocolo PCIe 5.0 reduz automaticamente a velocidade para Gen4 ou Gen3 para evitar corrupção de dados, muitas vezes sem aviso óbvio.

- A física mudou: Em 32 GT/s, as trilhas de cobre na placa-mãe (PCB) agem como filtros que destroem o sinal. O uso de cabos dedicados (MCIO/SlimSAS) e chips Retimers é obrigatório em distâncias médias.

- Diagnóstico via software: Antes de abrir o chassi, comandos como

lspcie logs de AER revelam se o problema é físico (camada PHY) ou lógico.

A física implacável dos 32 GT/s

Para entender por que seus drives estão falhando ou operando abaixo da capacidade, precisamos olhar para a frequência. O PCIe 4.0 operava com uma frequência de Nyquist de 8 GHz. O PCIe 5.0 dobrou isso para 16 GHz.

Na prática, isso significa que a margem de erro para ruído, jitter (variação no tempo de chegada do sinal) e perda de inserção (atenuação do sinal) diminuiu drasticamente. O material padrão de PCBs (FR4) é basicamente uma esponja absorvedora de sinal nessas frequências.

Se você tem um servidor onde o sinal precisa sair da CPU, percorrer 15 cm de trilha na placa-mãe, passar por um conector, subir por um riser e entrar no SSD, você tem um pesadelo de engenharia. É aqui que ocorre o fenômeno da "perda de inserção". Se o sinal chegar ao destino fraco demais, o receptor do SSD não consegue distinguir um "0" de um "1".

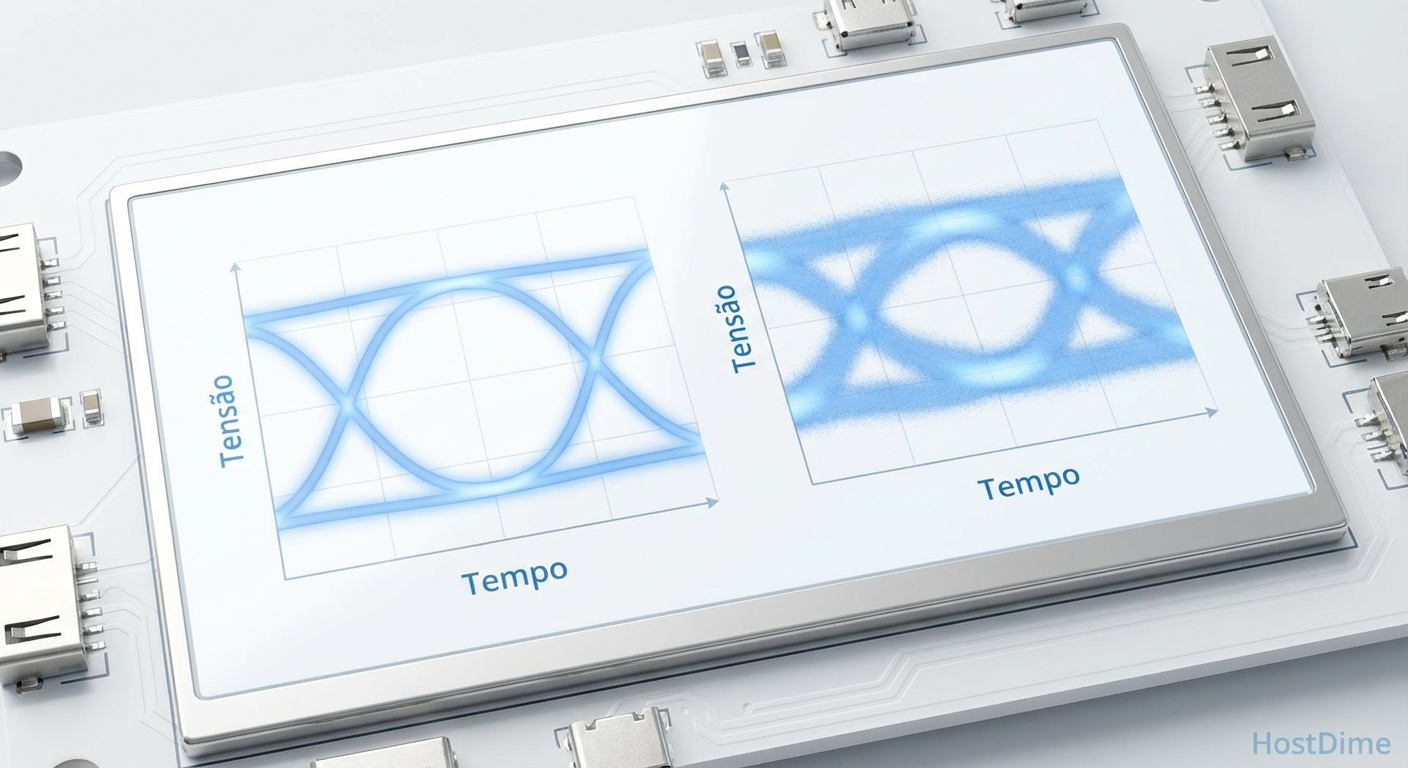

Figura: O diagrama de olho (eye diagram) ilustra a degradação do sinal: à esquerda, um sinal limpo; à direita, o "olho fechado" causado pela perda de inserção e ruído em longas distâncias no PCIe 5.0.

Figura: O diagrama de olho (eye diagram) ilustra a degradação do sinal: à esquerda, um sinal limpo; à direita, o "olho fechado" causado pela perda de inserção e ruído em longas distâncias no PCIe 5.0.

💡 Dica Pro: Em servidores modernos, evite "zip ties" (abraçadeiras plásticas) apertadas demais em cabos de dados de alta velocidade (MCIO/SlimSAS). A compressão altera a impedância do cabo no ponto de aperto, criando reflexões de sinal que matam a performance do Gen5.

Quando o link negocia para baixo (Downgrading)

O protocolo PCIe é resiliente. Durante a inicialização, ocorre o processo de Link Training. A CPU e o SSD conversam para determinar a maior velocidade possível que o canal físico suporta.

Se o canal estiver "sujo" (muita interferência ou perda), eles não vão travar a máquina. Eles vão concordar em falar mais devagar. É comum encontrar SSDs Gen5 operando em modo Gen3 (8 GT/s) ou com largura de banda reduzida (x2 em vez de x4).

O sintoma para o usuário é "lentidão". O diagnóstico real é falha na camada física.

Verificando a negociação no Linux

Não confie no que a caixa diz. Pergunte ao barramento. O comando lspci é seu multímetro digital aqui.

sudo lspci -vv -s 01:00.0 | grep -E "LnkCap|LnkSta"

Você procura por duas linhas:

LnkCap (Link Capabilities): O que o drive pode fazer (ex: Speed 32GT/s, Width x4).

LnkSta (Link Status): O que o drive está fazendo agora.

Se LnkCap diz 32GT/s e LnkSta diz 16GT/s ou 8GT/s, você tem um problema físico, não de software.

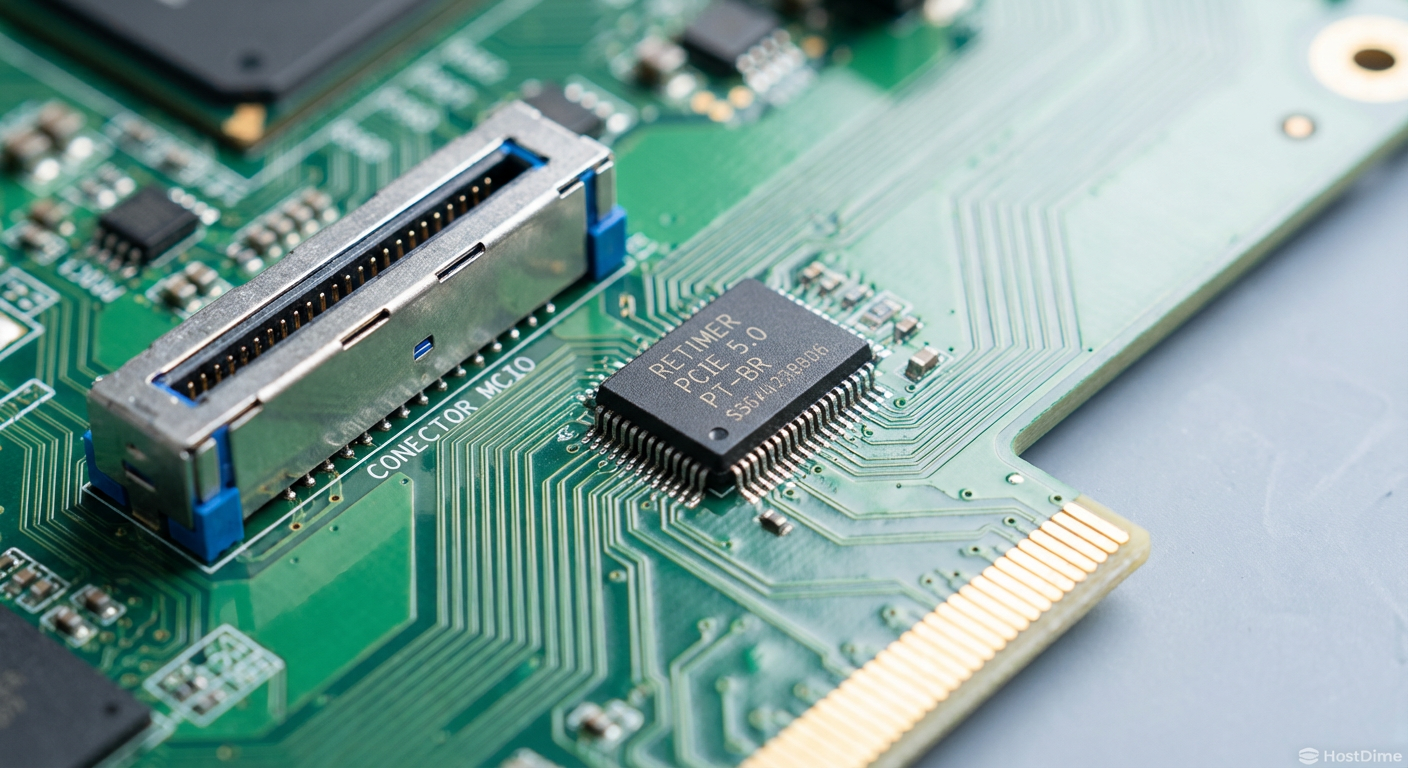

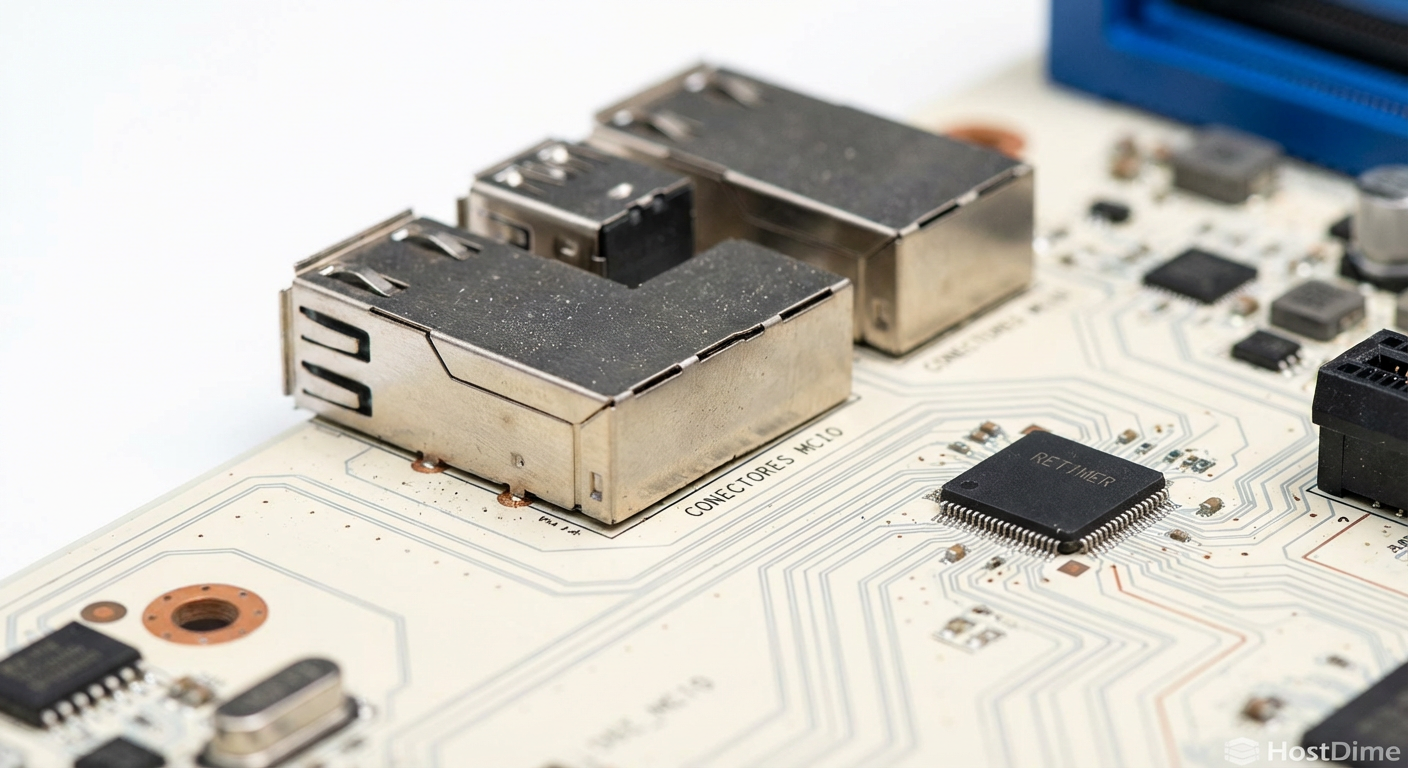

Figura: Detalhe de conectores MCIO e um chip Retimer em uma placa-mãe de servidor, componentes críticos para manter a integridade do sinal em conexões PCIe 5.0.

Figura: Detalhe de conectores MCIO e um chip Retimer em uma placa-mãe de servidor, componentes críticos para manter a integridade do sinal em conexões PCIe 5.0.

A topologia moderna: Retimers e cabos MCIO

Para combater a física, os fabricantes de servidores (Dell, HPE, Supermicro, Gigabyte) mudaram a arquitetura. Trilhas longas na placa-mãe morreram.

Hoje, vemos a ascensão do cabeamento direto e dos Retimers.

Cabos MCIO (Mini Cool Edge IO): São os sucessores dos cabos SAS/SATA, mas blindados para frequências extremas. Eles levam o sinal da placa-mãe direto para o backplane dos discos, "pulando" o PCB da placa-mãe.

Retimers vs. Redrivers:

- Um Redriver é um amplificador burro. Ele pega o sinal (e o ruído junto), aumenta o volume e repassa. Funciona bem para PCIe 3.0/4.0 curto.

- Um Retimer (obrigatório em rotas longas de PCIe 5.0) é inteligente. Ele decodifica o sinal, joga fora o ruído, recria o clock e retransmite uma cópia perfeita.

Se o seu servidor usa risers passivos longos sem retimers para drives Gen5, você terá problemas de estabilidade.

Tabela Comparativa: Desafios Físicos por Geração

| Característica | PCIe 3.0 (Legado) | PCIe 4.0 (Atual/Maduro) | PCIe 5.0 (Bleeding Edge) |

|---|---|---|---|

| Taxa de Transferência | 8 GT/s | 16 GT/s | 32 GT/s |

| Perda de Sinal Aceitável | -22 dB | -28 dB | -36 dB (Muito restrito) |

| Material do PCB | FR4 Padrão | FR4 de Alta Qualidade / Megtron 4 | Megtron 6 ou equivalente (Baixa perda) |

| Conexão Preferida | Trilhas na Placa | Trilhas Curtas / Cabos | Cabos MCIO/DAC / Retimers |

| Sensibilidade a Poeira | Baixa | Média | Alta (Contatos sujos causam link drop) |

Interpretando os logs de AER (Advanced Error Reporting)

Antes de trocar peças, verifique se o sistema está gritando por socorro. O AER é um mecanismo do padrão PCIe que reporta erros de integridade.

No Linux, use o dmesg para caçar esses fantasmas:

dmesg | grep -i "AER"

Você encontrará dois tipos principais de erros:

Correctable Errors (CE): O hardware detectou um bit errado, mas o código de correção de erro (ECC) do protocolo PCIe resolveu. O sistema não trava, mas a latência dispara porque o pacote precisou ser retransmitido (Replay). Se você vê milhares de "Replay Timer Timeout", seu cabo ou conector está ruim.

Uncorrectable Errors (UE): O dado foi corrompido além da recuperação. Isso geralmente resulta em um reset do link (o drive some e volta) ou uma tela azul/kernel panic.

⚠️ Perigo: Um drive que apresenta milhares de "Correctable Errors" é pior para a performance do cluster do que um drive morto. Ele causa "latência de cauda" (tail latency), fazendo com que requisições que deveriam levar microssegundos levem milissegundos, travando bancos de dados inteiros enquanto esperam a retransmissão.

Figura: Correlação direta: logs de erro AER no terminal Linux (esquerda) muitas vezes apontam para problemas físicos simples, como conectores sujos ou cabos degradados (direita).

Figura: Correlação direta: logs de erro AER no terminal Linux (esquerda) muitas vezes apontam para problemas físicos simples, como conectores sujos ou cabos degradados (direita).

O checklist do mecânico para PCIe 5.0

Se você diagnosticou instabilidade no link ou downgrade de velocidade, siga este roteiro antes de condenar o SSD:

Reseat (Reencaixe): A tolerância mecânica dos conectores Gen5 é minúscula. Um drive mal encaixado no backplane pode conectar, mas com ruído. Remova e insira firmemente.

Limpeza de Contatos: Poeira é condutiva ou isolante, dependendo da umidade. Em 32 GT/s, uma partícula de poeira no pino de transmissão (Tx) é fatal. Ar comprimido no backplane é essencial.

Verifique o Firmware do Backplane: Sim, o backplane (a placa onde os discos encaixam) muitas vezes tem um chip switch PCIe ou um expansor que possui firmware próprio. Atualize-o.

Troca de Cabo MCIO: Se o erro persiste em um slot específico mesmo trocando o SSD de lugar, o culpado provável é o cabo que liga a placa-mãe a esse slot. Cabos MCIO são frágeis; dobras excessivas quebram a blindagem interna.

O futuro não perdoa falhas físicas

Estamos caminhando para o PCIe 6.0, que utilizará sinalização PAM4 (quatro níveis de voltagem em vez de dois) para atingir 64 GT/s. Se você acha que o diagnóstico físico é chato ou difícil no Gen5, saiba que ele se tornará a habilidade mais valiosa no datacenter nos próximos anos.

A era de "apenas plugar e funcionar" acabou para o armazenamento de alta performance. Agora, você precisa entender o caminho que os elétrons percorrem. Mantenha seus conectores limpos, seus cabos sem dobras agudas e seus olhos nos logs de AER.

Referências & Leitura Complementar

PCI-SIG: PCI Express Base Specification Revision 5.0 (Foco em Camada Física).

OCP (Open Compute Project): Datacenter NVMe SSD Specification (Requisitos de conector e form factor).

NVM Express: Base Specification 2.0 (Gerenciamento de erros e logs).

Perguntas Frequentes (FAQ)

O que causa a queda de velocidade de um NVMe PCIe 5.0 para Gen4 ou Gen3?

Geralmente é uma falha no "Link Training". Se a integridade do sinal (Signal Integrity) não for suficiente para sustentar 32 GT/s devido a cabos ruins, poeira nos contatos ou perda de inserção excessiva na trilha da placa, o controlador negocia uma velocidade inferior para manter a estabilidade e evitar corrupção de dados.Qual a diferença prática entre Retimer e Redriver no PCIe 5.0?

O Redriver é um componente analógico simples que apenas amplifica o sinal (incluindo o ruído que ele carrega). O Retimer é um dispositivo digital inteligente que decodifica o sinal, limpa o jitter, recria o clock e retransmite uma cópia limpa. Para trilhas longas em Gen5, o Retimer é praticamente obrigatório.Como verificar erros de PCIe no Linux?

Utilize o comando `lspci -vv` para ver o status atual do link (procure por `LnkSta`) e compare com a capacidade máxima (`LnkCap`). Além disso, verifique os logs do kernel com `dmesg | grep AER` para identificar erros reportados pelo mecanismo de *Advanced Error Reporting*, que indicam falhas físicas ou de transmissão.

Carlos Ornelas

Mecânico de Datacenter

"Vivo nos corredores frios instalando racks e organizando cabeamento estruturado. Para mim, a nuvem é feita de metal, silício e ventoinhas que precisam girar sem parar."