NVMe sobre CXL: Quebrando a barreira da latência de bloco no data center

Descubra como o Compute Express Link (CXL) está transformando SSDs em memória endereçável, eliminando o overhead do protocolo de bloco e redefinindo a hierarquia de storage.

Vamos ser honestos por um minuto. O protocolo NVMe (Non-Volatile Memory Express) foi a melhor coisa que aconteceu ao armazenamento desde que alguém decidiu que fitas magnéticas não deveriam ser a única opção para backups. Ele removeu o gargalo do AHCI e nos deu filas paralelas massivas. Mas, como bons arquitetos de nuvem insaciáveis, nós batemos em outra parede. E essa parede não é o hardware; é o protocolo.

Estamos viciados em IOPS e largura de banda, mas ignoramos o elefante na sala: a latência de software. Quando você está pagando uma fortuna por instâncias EC2 de alta performance ou servidores bare-metal on-premise, cada microssegundo gasto no kernel do sistema operacional é dinheiro jogado no lixo. É aqui que a conversa muda de "discos mais rápidos" para "mudança fundamental de arquitetura".

Resumo em 30 segundos

- O problema: O protocolo NVMe tradicional, baseado em blocos, atingiu um teto de latência devido ao overhead da pilha de software (interrupções, trocas de contexto).

- A solução: CXL (Compute Express Link) permite que dispositivos de armazenamento falem a linguagem da memória (load/store) em vez de bloco (read/write).

- O resultado: Uma nova camada de "Memory-Semantic SSDs" que oferece latência próxima à DRAM por uma fração do custo, eliminando a latência de cauda.

O teto de vidro do protocolo de bloco

Nós passamos a última década otimizando o armazenamento em bloco. Migramos de SAS/SATA para NVMe sobre PCIe. A largura de banda explodiu. O PCIe Gen5 oferece 32 GT/s por lane. Isso é lindo no papel e nos slides de marketing da Intel e AMD.

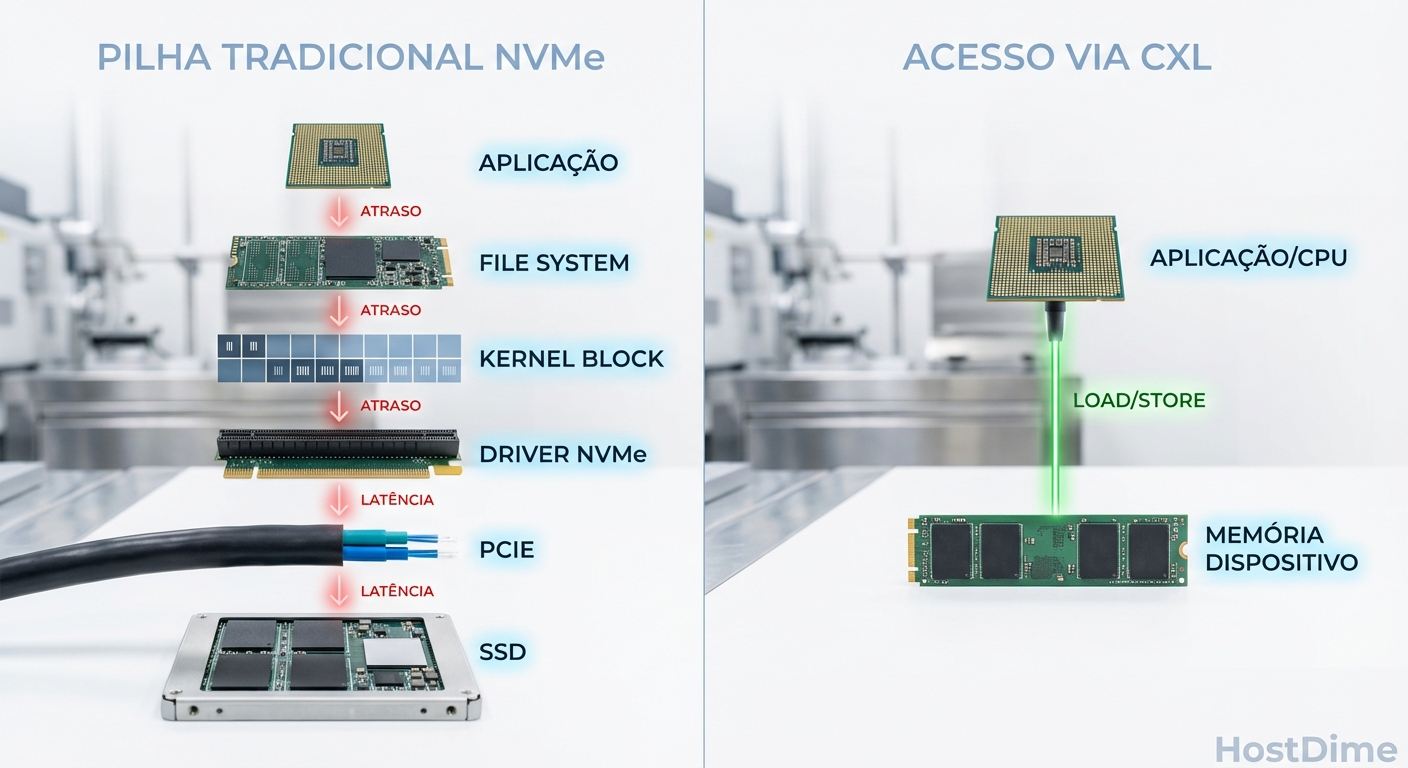

No entanto, a latência não escalou na mesma proporção. Por quê? Porque, no final do dia, o NVMe ainda é um protocolo de bloco. Para ler dados, sua CPU precisa:

Criar um comando de I/O.

Colocá-lo em uma fila de submissão.

Tocar a campainha (doorbell register) do dispositivo.

Esperar o SSD buscar os dados.

Lidar com uma interrupção quando os dados chegam.

Processar a fila de conclusão.

Isso é muita burocracia para ler 4KB de dados. Chamamos isso de "overhead da pilha de software". Em SSDs modernos (como os baseados em 3D XPoint ou NAND de ultra-baixa latência), o tempo que o software leva para pedir os dados começa a rivalizar com o tempo que o disco leva para entregá-los.

Figura: A anatomia do overhead: Enquanto o NVMe tradicional exige uma maratona pelo kernel, o CXL permite acesso direto via semântica de memória.

Figura: A anatomia do overhead: Enquanto o NVMe tradicional exige uma maratona pelo kernel, o CXL permite acesso direto via semântica de memória.

A revolução da semântica de memória

Aqui entra o CXL (Compute Express Link). Se você tem ignorado essa sigla esperando que ela desapareça como o Intel Optane (descanse em paz), acorde. O CXL é a mudança mais significativa na arquitetura de servidores desde a introdução do processador de 64 bits.

O CXL funciona sobre o barramento físico PCIe (a partir do Gen5), mas fala três protocolos diferentes. O que nos interessa aqui é o CXL.mem.

Com o CXL.mem, o dispositivo de armazenamento não é mais visto como um "disco" que precisa de drivers de bloco. Ele é mapeado diretamente no espaço de endereçamento físico da CPU. Isso significa que sua aplicação pode acessar dados no SSD usando instruções simples de CPU como MOV (Load/Store), exatamente como faz com a memória RAM DDR5.

💡 Dica Pro: Não confunda largura de banda com latência. Você pode ter um link de 1TB/s, mas se cada pacote demorar 10ms para começar a ser transmitido, seu banco de dados transacional vai sofrer. O CXL ataca a latência, não apenas a largura de banda.

Comparativo: Acesso em Bloco vs. Acesso em Memória

Para visualizar o impacto real, precisamos comparar como os dados trafegam nessas duas arquiteturas.

| Característica | NVMe Tradicional (Bloco) | NVMe sobre CXL (Memória) |

|---|---|---|

| Unidade de Acesso | Bloco (geralmente 4KB) | Byte (Cache Line de 64 bytes) |

| Mecanismo | DMA + Interrupções (Assíncrono) | Load/Store da CPU (Síncrono) |

| Overhead de Software | Alto (Kernel, Driver, Context Switch) | Quase Zero (Acesso direto ao hardware) |

| Latência Típica | ~80-100 µs (NAND padrão) | < 10-20 µs (Memory-Semantic SSD) |

| Coerência de Cache | Não (Gerenciado por SW) | Sim (Hardware garante coerência) |

O surgimento do "Memory-Semantic SSD"

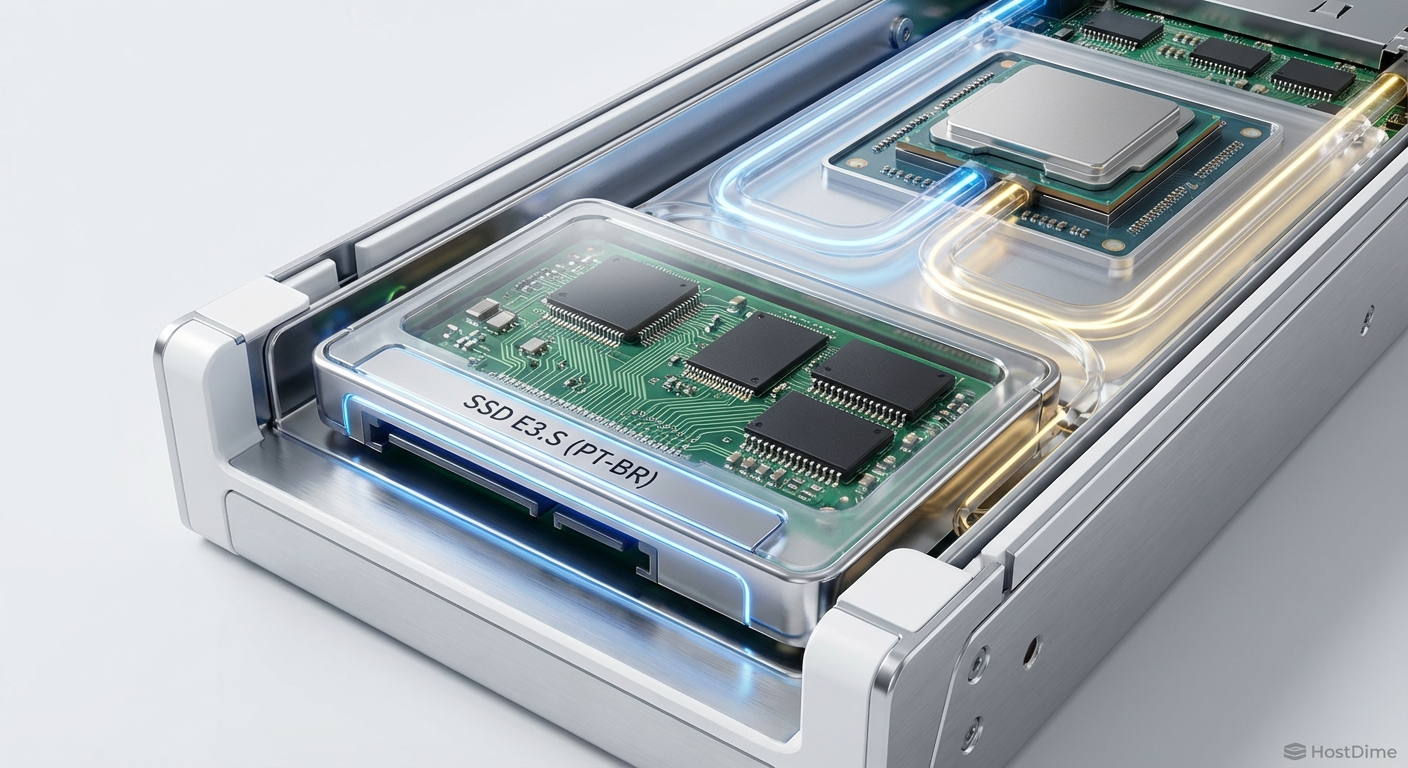

A indústria, liderada por players como Samsung e Kioxia, começou a desenvolver o que chamamos de "Memory-Semantic SSDs". Estes não são apenas SSDs rápidos; são dispositivos híbridos. Eles possuem um controlador CXL e utilizam uma combinação de DRAM interna (para cache ultra-rápido) e NAND Flash (para persistência).

O segredo aqui é o tamanho do acesso. Bancos de dados e aplicações de IA frequentemente precisam ler pequenos pedaços de dados (inferiores a 4KB). No NVMe tradicional, você é obrigado a ler o bloco inteiro de 4KB, desperdiçando largura de banda e ciclos de CPU. Com CXL, você lê apenas os 64 bytes que precisa.

Isso resolve o problema da amplificação de leitura. Se você precisa de 64 bytes mas lê 4096 bytes, você está movendo 64x mais dados do que o necessário. O CXL elimina esse desperdício.

Figura: O hardware híbrido: Dispositivos E3.S ou E1.S utilizando CXL combinam a persistência do Flash com a acessibilidade de byte da DRAM.

Figura: O hardware híbrido: Dispositivos E3.S ou E1.S utilizando CXL combinam a persistência do Flash com a acessibilidade de byte da DRAM.

Latência de cauda e o custo da nuvem

Vamos falar sobre dinheiro, porque é isso que importa quando a fatura da AWS chega. A latência média é uma métrica de vaidade. O que mata a experiência do usuário (e viola SLAs) é a latência de cauda (o percentil 99 ou p99).

Em sistemas de armazenamento tradicionais, a latência de cauda dispara devido a:

Garbage Collection do SSD: O disco está ocupado reorganizando blocos.

Contenção de Filas: O driver NVMe está saturado.

Interrupções de CPU: O processador está ocupado lidando com outra coisa.

Com CXL e semântica de memória, removemos a pilha de software e as interrupções do caminho crítico. O acesso é determinístico. Isso achata a curva de latência de cauda.

⚠️ Perigo: Ignorar a latência de cauda em arquiteturas de microsserviços é fatal. Se uma requisição precisa consultar 50 serviços e um deles engasga no storage, toda a requisição falha ou demora. O CXL atua como um seguro contra esses picos.

O novo Tier de Memória (Far Memory)

O caso de uso mais imediato não é substituir o SSD de boot, mas criar um novo tier de memória. Hoje temos:

Cache L1/L2/L3: Insanamente rápido, minúsculo.

DRAM (DDR5): Muito rápida, muito cara, capacidade limitada por soquete.

SSD NVMe: Rápido para disco, lento para memória, barato.

O CXL cria o Tier 2 de Memória (ou "Far Memory"). É um pool de memória ligeiramente mais lento que a DRAM local (cerca de 170-250ns de latência adicional), mas com capacidades de Terabytes e custo muito inferior. Para bancos de dados in-memory como Redis ou SAP HANA, isso é o Santo Graal. Você pode manter os dados "mornos" no CXL e os "quentes" na DDR5, tudo transparente para a aplicação.

O futuro não espera por drivers legados

Estamos caminhando para um data center desagregado. O modelo onde compramos um servidor com quantidade fixa de CPU, RAM e Disco está morrendo. Com CXL 3.0 e além, teremos "Pools de Memória" compartilhados entre vários servidores.

Se você projeta infraestrutura de storage, pare de pensar apenas em IOPS. Comece a pensar em coerência de cache e endereçamento de memória. A barreira entre "Armazenamento" e "Memória" está sendo demolida, tijolo por tijolo, pelo CXL. Quem continuar otimizando apenas para blocos de 4KB vai ficar para trás, pagando caro por DRAM que não precisa e lidando com latências que não deveria aceitar.

O NVMe sobre CXL não é apenas uma atualização de velocidade; é uma reescrita das regras de engajamento entre a CPU e seus dados.

Referências & Leitura Complementar

CXL Consortium: Compute Express Link™ (CXL™) 3.1 Specification (Lançada em 2023, definindo novos recursos de fabric e coerência).

SNIA (Storage Networking Industry Association): NVM Programming Model (NPM) Specifications (Documentação sobre como programar para memória persistente e novos modelos de acesso).

JEDEC: DDR5 & NVDIMM-P Standards (Essenciais para entender a base física onde o CXL opera em conjunto com a memória tradicional).

Samsung Semiconductor: Memory-Semantic SSD Technical Whitepaper (Detalhes sobre a implementação prática de CXL.mem em dispositivos NAND).

Perguntas Frequentes (FAQ)

O que é exatamente NVMe over CXL?

É uma arquitetura emergente que permite que dispositivos de armazenamento (SSDs) se comuniquem usando semântica de memória (load/store) via barramento CXL. Diferente do NVMe tradicional que usa protocolo de bloco (read/write), o CXL permite acesso direto e granular aos dados, reduzindo drasticamente a latência e o overhead de software.Qual a diferença técnica entre CXL.io e CXL.mem?

Pense no CXL.io como o "gerente": ele funciona de forma quase idêntica ao PCIe tradicional, usado para descoberta, configuração e gerenciamento do dispositivo. Já o CXL.mem é o "operário de elite": ele permite que a CPU acesse a memória do dispositivo diretamente com coerência de cache, o que é essencial para os novos "Memory-Semantic SSDs" funcionarem como expansão de RAM.O CXL vai matar a memória RAM DRAM tradicional?

Não, e nem deveria. O objetivo é expandir a capacidade e reduzir o TCO (Custo Total de Propriedade). O CXL cria um novo tier de memória (chamado de Tier 2 ou Far Memory) que é ligeiramente mais lento que a DRAM local conectada diretamente à CPU, mas é muito mais rápido e barato que um SSD NVMe convencional. É sobre hierarquia eficiente, não substituição total.

Rafael Barros

Arquiteto de Cloud Storage

"Desenho arquiteturas de object storage escaláveis e guiadas por API. Meu foco é performance máxima sem deixar o orçamento sangrar com taxas de egress ocultas."