O fim do gargalo de memória na IA: como módulos CXL 3.1 transformam servidores corporativos

Descubra como a desagregação de memória com módulos CXL 3.1 Type 3 resolve o limite de cache KV em clusters de IA, reduzindo custos de infraestrutura.

O boom da inteligência artificial generativa trouxe um problema grave para os corredores dos data centers. Enquanto o mercado foca obsessivamente na escassez de GPUs, os arquitetos de infraestrutura enfrentam um gargalo muito mais silencioso e limitante. A capacidade de memória dos servidores corporativos atingiu um teto físico. Para sustentar modelos de linguagem cada vez maiores, a indústria de hardware está mudando radicalmente a forma como pensamos sobre armazenamento temporário e memória RAM.

Resumo em 30 segundos

- Modelos de linguagem esgotam a memória RAM rapidamente devido ao cache KV durante a inferência.

- Limites físicos das placas-mãe impedem a simples adição de mais pentes DDR5 aos servidores.

- Módulos CXL 3.1 usam o barramento PCIe para expandir a memória em terabytes, criando uma nova arquitetura de infraestrutura.

A crise silenciosa dos data centers e o peso do cache KV

Quando você interage com uma inteligência artificial, o modelo precisa lembrar de tudo o que foi dito anteriormente na conversa para gerar respostas coerentes. Esse histórico de contexto é armazenado no que chamamos de cache KV (Key-Value Cache). Durante a fase de inferência, que é a geração da resposta em si, esse cache cresce de forma assustadora.

Quanto maior o documento analisado ou mais longa a conversa, mais gigabytes de memória são consumidos instantaneamente. Em clusters de IA corporativos que atendem milhares de usuários simultâneos, o cache KV esgota a memória RAM disponível muito antes de o processador ou a GPU atingirem seu limite de processamento. O servidor fica ocioso, esperando espaço na memória para continuar trabalhando.

Por que adicionar mais pentes DDR5 deixou de ser viável

A solução lógica seria simplesmente colocar mais pentes de memória nos servidores. No entanto, a arquitetura tradicional de placas-mãe chegou ao seu limite físico. Os processadores modernos possuem um número fixo de canais de memória. Adicionar mais slots DIMM para pentes DDR5 degrada a integridade do sinal elétrico, causando instabilidade no sistema.

⚠️ Perigo: Tentar contornar a falta de memória usando armazenamento NVMe tradicional para paginação (swap) destrói a performance da inferência de IA. A latência de um SSD, mesmo os mais rápidos, é ordens de grandeza maior que a da RAM, travando a geração de texto.

Os fabricantes de servidores se viram em um beco sem saída. Criar placas-mãe maiores e mais complexas aumentaria o custo de fabricação para níveis impraticáveis, além de gerar problemas severos de refrigeração dentro dos racks dos data centers.

O papel dos módulos CXL 3.1 na expansão via PCIe

A resposta da indústria para esse gargalo atende pela sigla CXL (Compute Express Link). Trata-se de um padrão aberto de interconexão apoiado por gigantes da tecnologia. O CXL utiliza a interface física do barramento PCIe, o mesmo usado para conectar placas de vídeo e placas de rede, para criar uma via de comunicação ultrarrápida entre a CPU e dispositivos externos.

Dentro desse ecossistema, os dispositivos CXL Type 3 são os verdadeiros divisores de águas. Eles são módulos de expansão de memória que se conectam aos slots PCIe do servidor. Para o sistema operacional e para o hypervisor, essa placa de expansão aparece exatamente como memória RAM nativa. Isso permite adicionar terabytes de capacidade a um servidor sem depender dos limitados slots DIMM da placa-mãe.

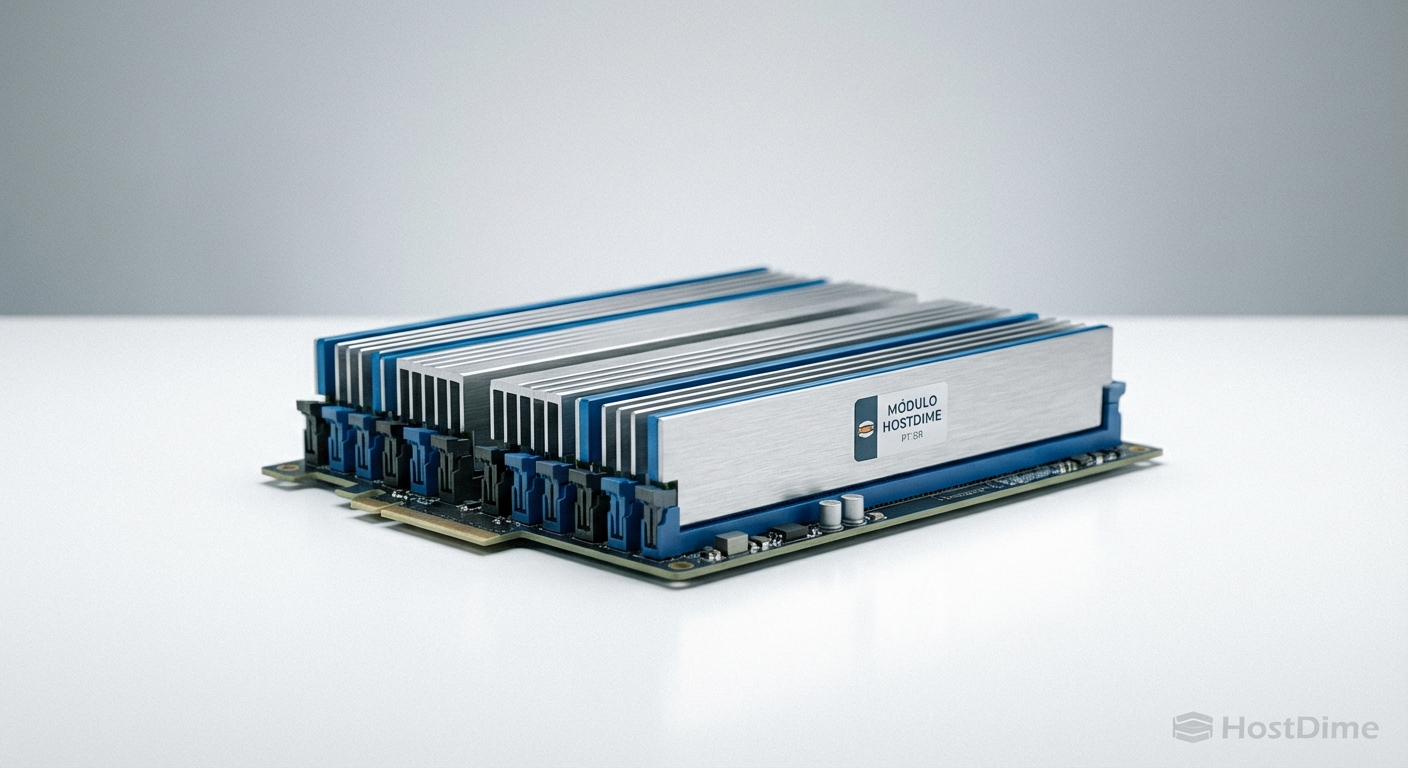

Figura: Renderização 3D de uma placa-mãe de servidor mostrando slots DDR5 lotados e placas de expansão CXL conectadas aos slots PCIe.

Figura: Renderização 3D de uma placa-mãe de servidor mostrando slots DDR5 lotados e placas de expansão CXL conectadas aos slots PCIe.

A versão 3.1 do protocolo CXL trouxe melhorias cruciais no roteamento de dados e na coerência de cache. Isso significa que múltiplos servidores podem, teoricamente, compartilhar o mesmo pool de memória CXL, algo impensável com a arquitetura DDR5 tradicional.

O custo oculto da latência e o tiering de memória

Apesar de revolucionária, a memória CXL não é mágica. Como os dados precisam viajar pelo barramento PCIe, existe um pequeno acréscimo de latência em comparação com a memória DDR5 conectada diretamente aos canais da CPU. Estamos falando de nanosegundos, mas em computação de alto desempenho, cada ciclo de clock importa.

Para resolver isso, a arquitetura de storage e memória adotou o conceito de tiering (camadas). A memória DDR5 nativa atua como a camada quente, processando os cálculos imediatos da IA. Já os módulos CXL atuam como a camada morna, armazenando o massivo cache KV e os pesos do modelo. O software gerencia a movimentação dos dados entre essas camadas de forma transparente.

| Característica | Memória DDR5 (DIMM) | Memória CXL 3.1 (Type 3) |

|---|---|---|

| Conexão | Slots nativos da placa-mãe | Barramento PCIe |

| Capacidade Máxima | Limitada pelos canais da CPU | Escalável em múltiplos Terabytes |

| Latência | Ultrabaixa (Acesso direto) | Baixa (Adiciona nanosegundos do PCIe) |

| Custo de Expansão | Alto (Exige troca de servidor) | Médio (Adição de placas PCIe) |

| Uso Ideal | Processamento em tempo real | Expansão massiva para cache KV e bancos de dados |

A transição para infraestruturas totalmente combináveis

A adoção do CXL 3.1 está pavimentando o caminho para o que a indústria chama de infraestrutura combinável (composable infrastructure). Em vez de comprar um servidor fechado com quantidades fixas de CPU, RAM e disco, os data centers estão migrando para racks onde esses recursos são separados em blocos independentes.

💡 Dica Pro: Softwares de virtualização e hypervisors modernos já estão sendo atualizados para reconhecer a memória CXL nativamente. Isso permite que administradores de TI aloquem fatias dessa memória expandida para diferentes máquinas virtuais sob demanda, otimizando o custo por gigabyte.

Se um cluster de IA precisar de mais memória para uma carga de trabalho específica amanhã, o administrador não precisará desligar o servidor para instalar novos pentes. Ele simplesmente alocará mais capacidade do pool de memória CXL via software.

O que esperar da próxima geração de servidores

A barreira da memória foi rompida. A recomendação para arquitetos de infraestrutura e gestores de TI é clara. Ao planejar a renovação do parque de servidores para os próximos ciclos, a compatibilidade com PCIe 5.0 e suporte nativo ao protocolo CXL devem ser requisitos inegociáveis.

Servidores que dependem exclusivamente de slots DIMM tradicionais se tornarão obsoletos rapidamente frente às demandas de memória da inteligência artificial. O armazenamento corporativo deixou de ser apenas sobre discos e SSDs. A memória RAM agora é um recurso elástico, e o CXL é a ferramenta que tornou isso possível.

O que é um módulo de memória CXL Type 3?

É um dispositivo de expansão de memória que se conecta ao servidor através do barramento PCIe, permitindo adicionar terabytes de capacidade sem depender dos slots DIMM tradicionais da placa-mãe.Por que o cache KV é um problema para clusters de IA?

Durante a geração de respostas (inferência), modelos de IA armazenam o contexto da conversa no cache KV. Quanto maior o texto processado, mais memória é consumida, esgotando rapidamente os recursos físicos do servidor.A memória CXL substitui a memória RAM tradicional?

Não. A memória CXL atua como uma camada de expansão (tiering). A RAM tradicional continua sendo usada para processos que exigem latência ultrabaixa, enquanto o CXL lida com o volume massivo de dados.

Mariana Costa

Repórter de Tecnologia (Newsroom)

"Cubro o universo de TI corporativa com agilidade jornalística. Minha missão é traduzir o 'tech-speak' de datacenters e cloud em notícias diretas para sua tomada de decisão."