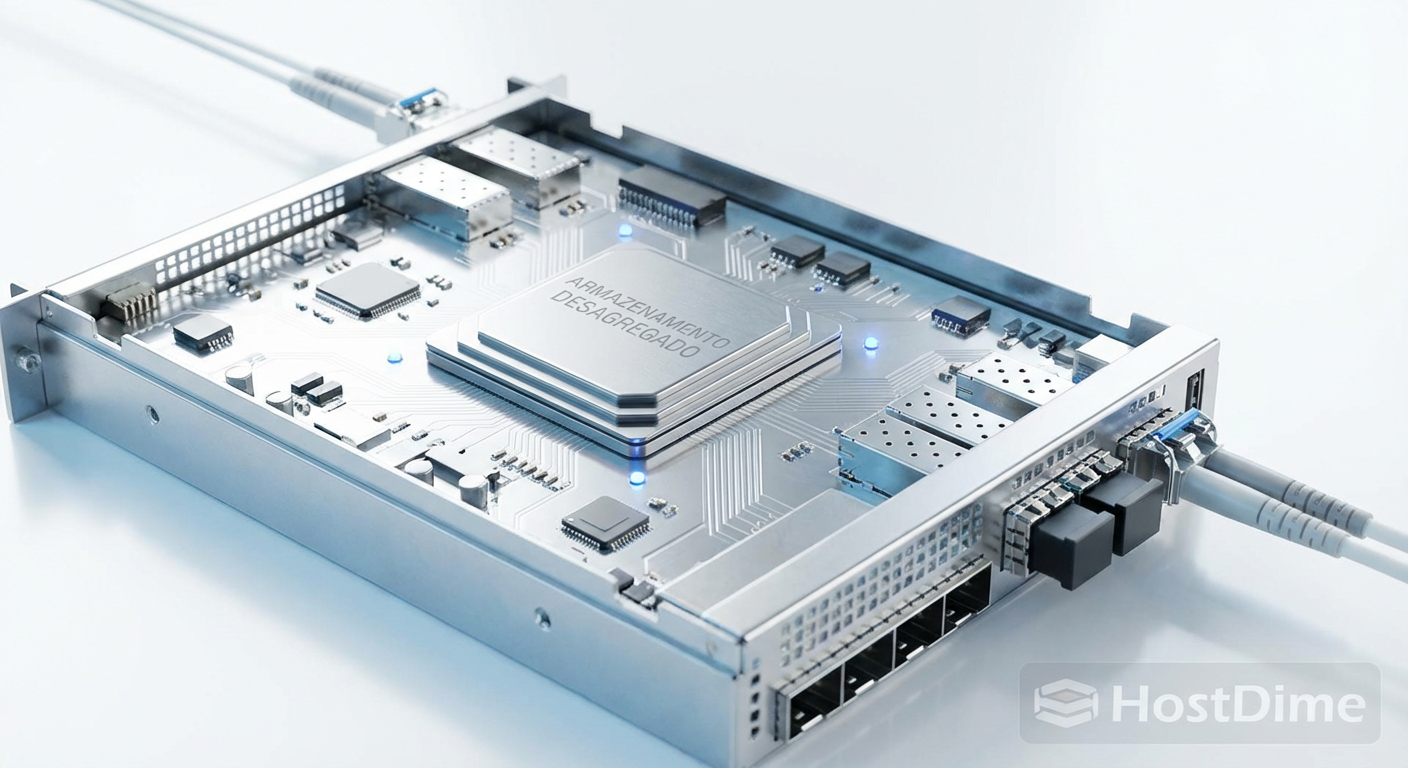

O fim do "imposto" da CPU: como as DPUs reescrevem a arquitetura NVMe-oF

Análise técnica de como as DPUs eliminam o overhead de interrupções em arquiteturas NVMe over Fabrics, permitindo storage desagregado com performance de DAS e latência determinística.

Você comprou um servidor com 128 núcleos, pagou uma fortuna em licenças de software por soquete e, no final do dia, descobre que 30% da sua capacidade de computação está sendo usada apenas para mover dados de um lugar para outro. Parabéns, você acabou de conhecer o "imposto" da CPU. No mundo do armazenamento de alto desempenho, especialmente com a ascensão do NVMe over Fabrics (NVMe-oF), a CPU de propósito geral (x86) se tornou o gargalo mais caro e ineficiente do data center.

Estamos vivendo uma mudança tectônica. A ideia de que a CPU central deve gerenciar tudo — da lógica da aplicação ao handshake do TCP e à criptografia do disco — é uma relíquia arquitetônica. É aqui que entram as DPUs (Data Processing Units). Elas não são apenas "placas de rede mais espertas"; elas são a admissão de que a Lei de Moore não consegue mais acompanhar a velocidade dos nossos SSDs e redes de 400Gbps. Vamos dissecar como isso muda o jogo do storage e por que seu próximo cluster de armazenamento provavelmente não dependerá da CPU do host para quase nada.

Resumo em 30 segundos

- O Problema: Processar protocolos de rede (TCP/IP) e armazenamento (NVMe) em CPUs x86 consome ciclos valiosos, criando o "imposto do data center".

- A Solução: DPUs (como NVIDIA BlueField ou AMD Pensando) isolam o host, processando todo o stack de storage no hardware dedicado.

- O Resultado: Latência determinística, liberação de 100% da CPU do host para aplicações e viabilidade real do NVMe/TCP sem a complexidade do RDMA.

A matemática cruel das interrupções e o colapso do x86

Para entender por que precisamos de DPUs, precisamos olhar para o que acontece quando um pacote de dados chega ao seu servidor. Em uma arquitetura tradicional, a placa de rede (NIC) recebe o pacote e gera uma interrupção. A CPU para o que está fazendo (context switch), copia os dados da memória da placa para a memória do sistema, processa o cabeçalho TCP, verifica a integridade (checksum), descriptografa (TLS) e, finalmente, entrega o payload para a aplicação ou sistema de arquivos.

Isso funcionava bem quando tínhamos redes de 1Gbps e HDDs girando a 7200 RPM. Hoje, com links de 100Gbps ou 200Gbps e SSDs NVMe capazes de milhões de IOPS, a CPU é bombardeada.

💡 Dica Pro: A regra de ouro não dita da indústria é que você precisa de aproximadamente 1 núcleo de CPU x86 moderno para cada 10-15 Gbps de tráfego TCP/IP processado via software. Faça as contas para um link de 200Gbps e veja seu orçamento de computação evaporar.

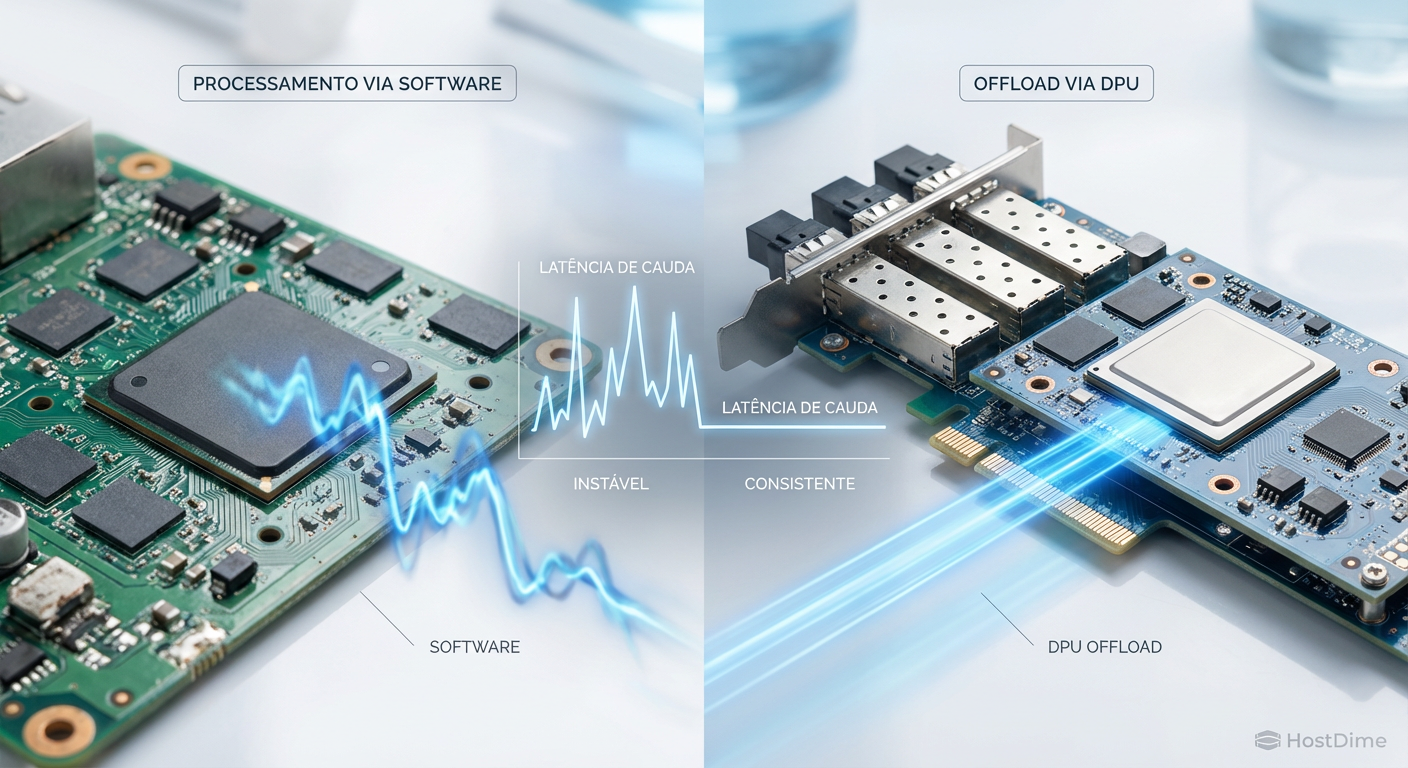

Esse fenômeno cria o que chamamos de "Noisy Neighbor" (vizinho barulhento) no nível do silício. O processamento de I/O (Entrada/Saída) compete pelos mesmos ciclos de clock, cache L3 e largura de banda de memória que seu banco de dados ou aplicação de IA. O resultado? Latência de cauda (P99) imprevisível.

Figura: O gargalo do I/O: Visualização de como o tráfego de rede e interrupções saturam os núcleos da CPU, deixando poucos recursos para a aplicação real.

Figura: O gargalo do I/O: Visualização de como o tráfego de rede e interrupções saturam os núcleos da CPU, deixando poucos recursos para a aplicação real.

O que é uma DPU e por que ela não é apenas uma SmartNIC

O termo "SmartNIC" foi abusado pelo marketing por anos para descrever qualquer placa de rede que pudesse fazer um offload básico de checksum. Uma DPU (Data Processing Unit) é uma besta diferente.

Uma DPU é, essencialmente, um servidor completo dentro do seu servidor. Ela possui:

Núcleos de Processamento Próprios: Geralmente ARM (como na NVIDIA BlueField) ou MIPS/P4 (como na AMD Pensando), rodando seu próprio sistema operacional (frequentemente um Linux completo).

Aceleradores de Hardware: Blocos de silício dedicados para criptografia (IPsec/TLS), compressão, e o mais importante para nós: NVMe-oF.

Conectividade de Alta Velocidade: Interfaces de rede de 100/200/400Gbps e pistas PCIe Gen4 ou Gen5 para conectar ao host.

A diferença fundamental é o isolamento. Em uma SmartNIC tradicional, o driver ainda roda no host. Na DPU, o stack de armazenamento roda na placa. Para o sistema operacional do servidor (host), o armazenamento remoto aparece como se fosse um disco NVMe local. O host não sabe — e não se importa — se os dados estão vindo via TCP, RoCE ou InfiniBand. A DPU abstrai toda a complexidade da "fabric".

Tabela comparativa: a evolução do offload

| Característica | NIC Padrão | SmartNIC (FPGA/ASIC básico) | DPU (Data Processing Unit) |

|---|---|---|---|

| Processamento de Protocolo | CPU do Host (Software) | Parcial (Offload de stateless) | Total (Full Stack na DPU) |

| Impacto na CPU do Host | Alto (Interrupções massivas) | Médio | Quase Zero |

| Programabilidade | Nenhuma | Limitada (Firmware/P4) | Alta (Linux, C++, P4, DOCA) |

| Isolamento de Segurança | Nenhum | Baixo | Total (Air-gap lógico) |

| Caso de Uso Principal | Conectividade básica | Filtragem de pacotes simples | Storage definido por software, Zero Trust |

NVMe/TCP: a redenção através do hardware

Durante anos, a batalha do NVMe over Fabrics foi travada entre a simplicidade do TCP e a performance do RDMA (RoCE v2).

RoCE (RDMA over Converged Ethernet): Oferece latência ultrabaixa e bypass de CPU, mas exige uma rede "Lossless" (sem perda de pacotes), configurada com PFC (Priority Flow Control) e ECN. É um pesadelo para gerenciar em escala. Um switch mal configurado pode derrubar o cluster.

NVMe/TCP: Roda em qualquer rede Ethernet padrão. É robusto e escalável. O problema? O overhead do TCP na CPU é brutal. O cálculo de CRC e a remontagem de pacotes matam a performance.

A DPU resolve esse dilema. Ela implementa o stack NVMe/TCP em hardware. A DPU termina a conexão TCP, verifica os CRCs, remonta os dados e os escreve diretamente na memória do host via DMA (Direct Memory Access).

⚠️ Perigo: Tentar rodar NVMe/TCP de alta performance (100Gbps+) sem offload de hardware é pedir para transformar seus servidores de aplicação em aquecedores glorificados. Você verá latências de disco flutuando violentamente dependendo da carga da CPU.

Com a DPU, o NVMe/TCP atinge paridade de performance com o RoCE, mas mantendo a simplicidade da infraestrutura de rede Ethernet padrão. Você não precisa mais de switches caros com buffers profundos ou configurações esotéricas de QoS.

Figura: Comparativo de Latência de Cauda: A instabilidade do processamento via software versus a consistência determinística do offload via DPU.

Figura: Comparativo de Latência de Cauda: A instabilidade do processamento via software versus a consistência determinística do offload via DPU.

O futuro da composabilidade e o papel do CXL

Se olharmos um pouco além, a DPU é a peça chave para a infraestrutura composável. Com a chegada do CXL (Compute Express Link) — um padrão de interconexão de alta velocidade que mantém a coerência de cache entre CPU e dispositivos —, a distinção entre "memória local" e "memória remota" começa a desaparecer.

No futuro próximo, as DPUs não apenas apresentarão volumes de disco, mas também faixas de memória. Imagine um chassi cheio de RAM e SSDs gerenciado por DPUs, entregando recursos sob demanda para servidores de computação via CXL sobre fibra. O servidor monolítico, onde você compra CPU, RAM e Storage em uma caixa fechada, está com os dias contados. A DPU é o controlador de tráfego dessa nova arquitetura desagregada.

O veredito do arquiteto

Não saia correndo para colocar DPUs em servidores de arquivos simples ou em nós que mal saturam um link de 10Gbps; a conta não fecha. A DPU brilha onde a densidade de I/O é crítica: hypervisors de nuvem, nós de banco de dados de alta performance e clusters de armazenamento definido por software (SDS) como Ceph ou MinIO.

A realidade é que o modelo centrado na CPU x86 atingiu um muro de escalabilidade. Continuar jogando núcleos de processador geral em problemas de infraestrutura de I/O é financeiramente irresponsável. As DPUs reescrevem essa equação, permitindo que você pague pela CPU para rodar sua aplicação, não para mover bits. Se você está desenhando a próxima geração do seu data center privado ou avaliando instâncias de nuvem (como as baseadas em AWS Nitro), a presença de offload dedicado de storage não é mais um luxo, é um requisito de arquitetura.

Referências & Leitura Complementar

NVM Express Base Specification 2.0: Documentação oficial sobre os transportes NVMe, incluindo TCP e RDMA.

NVIDIA DOCA SDK Documentation: Detalhes técnicos sobre como a arquitetura BlueField realiza o offload de NVMe SNAP (Software-defined Network Accelerated Processing).

SNIA (Storage Networking Industry Association): Whitepapers sobre a eficiência energética e de performance do offload de armazenamento.

RFC 9304: Especificação técnica do protocolo NVMe over TCP.

Perguntas Frequentes (FAQ)

Qual a diferença real entre uma SmartNIC e uma DPU para storage?

Enquanto SmartNICs realizam offloads parciais de rede (como checksum ou filtragem básica), as DPUs possuem núcleos programáveis completos (geralmente ARM) e memória própria. Elas rodam todo o sistema operacional e o stack NVMe-oF internamente, isolando completamente o host do processamento de I/O e apresentando o armazenamento remoto como se fosse um dispositivo local.O NVMe/TCP com DPU consegue competir com RoCE v2?

Sim. O grande gargalo do NVMe/TCP sempre foi o overhead de CPU para processar o protocolo. Com o processamento do TCP descarregado nos aceleradores da DPU, a latência e o consumo de recursos se tornam comparáveis ao RDMA (RoCE), mas com a vantagem de usar switches Ethernet padrão sem as configurações complexas de Lossless Network.Preciso reescrever minhas aplicações para usar uma DPU?

Geralmente não. A beleza da arquitetura de DPU moderna é que ela expõe o armazenamento para o sistema operacional do host como um dispositivo de bloco NVMe padrão (via PCIe). Sua aplicação ou banco de dados vê um "disco local" e interage com ele normalmente, sem saber que toda a mágica de rede e virtualização está acontecendo na placa.

Rafael Barros

Arquiteto de Cloud Storage

"Desenho arquiteturas de object storage escaláveis e guiadas por API. Meu foco é performance máxima sem deixar o orçamento sangrar com taxas de egress ocultas."