O fim do servidor monolítico: como o CXL 3.0 reescreve a arquitetura do datacenter

A placa-mãe morreu. Descubra como o CXL 3.0, PCIe 6.0 e a desagregação de memória estão transformando o rack na nova unidade de computação.

O fim do servidor monolítico: como o CXL 3.0 reescreve a arquitetura do datacenter

A placa-mãe, como a conhecemos, é um artefato histórico prestes a se tornar obsoleto. Durante décadas, aceitamos o dogma de que a CPU, a memória e o armazenamento devem residir na mesma caixa de metal, limitados pelas trilhas de cobre impressas em uma placa de circuito de fibra de vidro. Essa arquitetura, embora tenha nos servido bem desde a era dos mainframes, atingiu um muro de concreto físico e econômico.

Estamos testemunhando a dissolução do servidor como uma unidade discreta. O futuro da infraestrutura não é sobre caixas mais rápidas; é sobre a desintegração dessas caixas em recursos fluidos e compartilháveis. O catalisador dessa mudança tectônica é o Compute Express Link (CXL), especificamente em sua iteração 3.0. Não se trata apenas de um novo cabo ou protocolo; é a reescrita fundamental de como os bits viajam, são armazenados e processados. O datacenter está deixando de ser um armazém de computadores para se tornar, ele próprio, o computador.

Resumo em 30 segundos

- O Fim do Desperdício: O CXL 3.0 permite o "Memory Pooling", onde a RAM não fica mais presa a uma CPU específica, resolvendo o problema de "Stranded Memory" que custa bilhões aos hyperscalers.

- Velocidade da Luz (Quase): Baseado no PCIe 6.0, o CXL 3.0 dobra a largura de banda para 64 GT/s usando codificação PAM-4, permitindo que memórias externas tenham latência próxima à das memórias locais.

- A Nova Topologia: A arquitetura muda de "Servidor-Centrica" para "Data-Centrica", onde CPUs, GPUs e Storage acessam um pool de memória compartilhado via um fabric comutado, eliminando gargalos de I/O.

A morte da placa-mãe como limite físico

A arquitetura atual de servidores é inerentemente ineficiente. Imagine que você comprou uma casa (o servidor) com 10 quartos (núcleos de CPU) e uma garagem para 2 carros (Memória RAM). Se você tiver uma festa com 50 pessoas (carga de trabalho intensiva em memória), a garagem lota, mas os quartos ficam vazios. Você é obrigado a comprar outra casa inteira só para ter mais garagem.

Isso é o que chamamos de Stranded Memory (Memória Encalhada). Em datacenters de hiperescala, como os da Azure ou AWS, estima-se que até 50% da DRAM instalada nunca é utilizada porque os núcleos da CPU atingem 100% de uso antes que a memória seja preenchida, ou vice-versa. A memória fica "presa" na ilha daquele servidor específico.

O CXL 3.0 quebra as paredes dessa casa. Ele desacopla a memória da CPU. A placa-mãe deixa de ser o limite. A memória passa a ser um recurso de rede, acessível por qualquer processador no rack ou no cluster, com coerência de cache mantida via hardware.

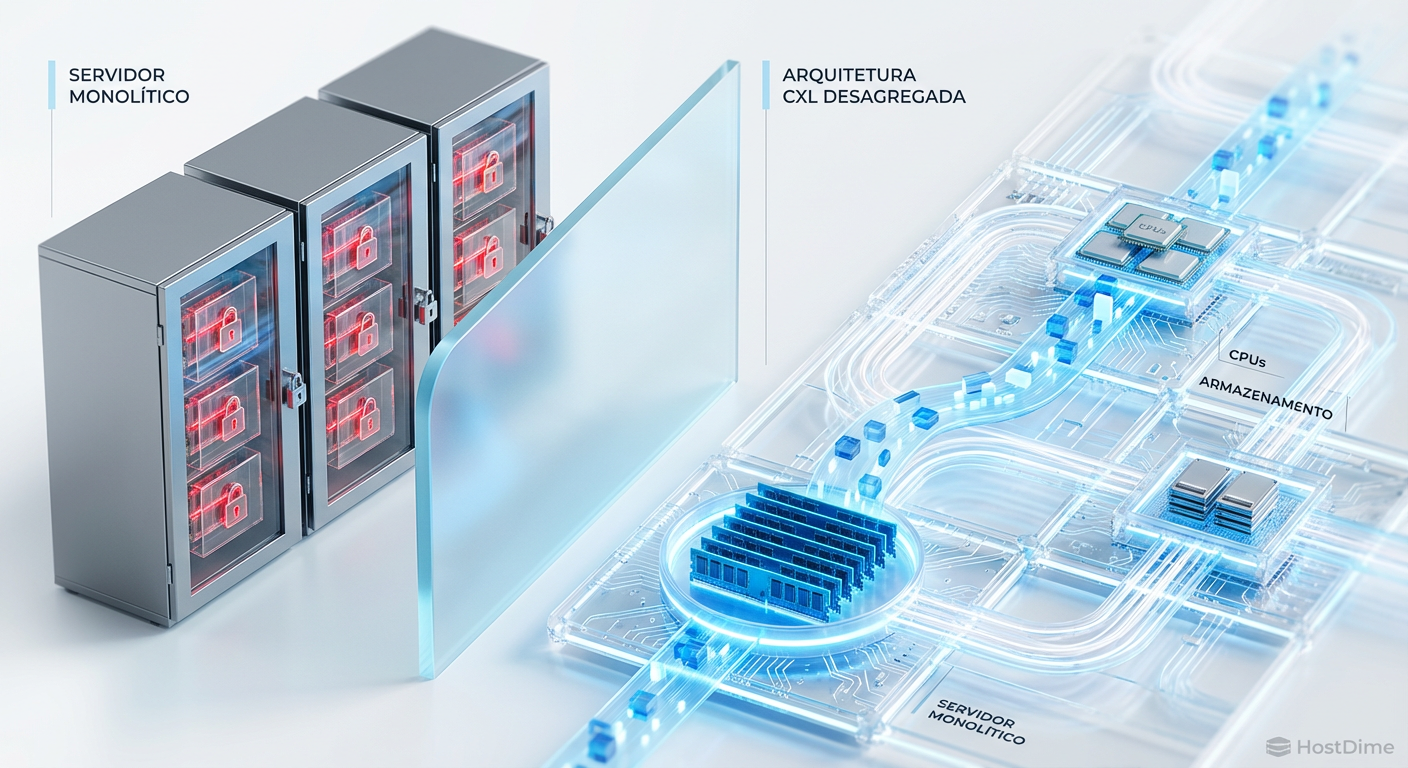

Figura: Comparativo visual: A rigidez do servidor tradicional com recursos presos versus a fluidez da arquitetura desagregada via CXL.

Figura: Comparativo visual: A rigidez do servidor tradicional com recursos presos versus a fluidez da arquitetura desagregada via CXL.

A física por trás do salto: PCIe 6.0 e PAM-4

Para fazer a memória externa parecer local, a velocidade é inegociável. O CXL 3.0 é construído sobre a camada física do PCIe 6.0. Aqui, a engenharia bruta entra em cena. Para atingir 64 GT/s (Giga Transfers por segundo), o dobro da geração anterior, a indústria teve que abandonar a codificação binária simples (NRZ - Non-Return-to-Zero), que usava apenas 0s e 1s (baixa e alta voltagem).

Entra em cena o PAM-4 (Pulse Amplitude Modulation 4-level). Em vez de dois níveis de voltagem, usamos quatro. Isso permite transmitir dois bits por ciclo de clock em vez de um. É como adicionar mais faixas a uma rodovia sem alargar a estrada, apenas fazendo os carros andarem mais perto e de forma mais inteligente.

⚠️ Perigo: A complexidade do PAM-4 traz um desafio brutal: a integridade do sinal. Com quatro níveis de voltagem, a "margem de ruído" entre eles é muito menor. O sinal degrada muito mais rápido. É por isso que o Forward Error Correction (FEC) de baixa latência se tornou obrigatório, e a qualidade dos cabos e trilhas da PCB nunca foi tão crítica.

O renascimento do armazenamento: CXL como o novo SAN

Para os profissionais de storage, o CXL 3.0 é a maior mudança desde a invenção do NVMe. Até hoje, tratamos armazenamento (SSD/HDD) e memória (DRAM) como entidades distintas, separadas por um abismo de latência e protocolos (SATA/SAS/NVMe vs DDR).

O CXL introduz o conceito de Memory-Semantic SSDs. Imagine um SSD NVMe que não fala mais "blocos" (leia o setor X), mas fala "bytes" (leia o endereço de memória Y), diretamente no barramento de memória da CPU. Isso elimina a sobrecarga da pilha de software do sistema operacional (interrupções, trocas de contexto, drivers de sistema de arquivos).

Isso cria uma nova camada na hierarquia de armazenamento:

L1/L2/L3 Cache (SRAM na CPU)

DRAM Local (DDR5)

CXL Attached Memory (DRAM ou SCM expandida)

CXL Storage (SSDs de latência ultrabaixa)

NVMe SSDs Tradicionais (PCIe)

Cold Storage (HDD/Tape)

O CXL 3.0 permite que dispositivos de armazenamento conversem diretamente entre si (Peer-to-Peer) sem passar pela CPU host. Uma GPU pode puxar dados de um pool de SSDs CXL diretamente. Isso libera a CPU de ser o "policial de trânsito" do datacenter, função que hoje consome ciclos preciosos.

Tabela Comparativa: Arquitetura Tradicional vs. CXL 3.0

| Característica | Servidor Monolítico (Atual) | Arquitetura CXL 3.0 (Futuro Próximo) |

|---|---|---|

| Expansão de Memória | Limitada aos slots DIMM físicos da placa-mãe. | Virtualmente ilimitada via slots CXL e pools externos. |

| Utilização de Recursos | Baixa (Recursos presos/Stranded). | Alta (Alocação dinâmica sob demanda). |

| Latência de Acesso | Baixa (Local) a Alta (Rede/RDMA). | Baixa (Local) a Média-Baixa (CXL Fabric - ~200ns). |

| Comunicação | CPU-Centrica (Tudo passa pelo processador). | Data-Centrica (Dispositivos falam entre si/P2P). |

| Custo de Upgrade | Alto (Trocar servidor inteiro para ter mais RAM). | Baixo (Adicionar módulos ao pool de memória). |

A barreira do cobre e a ascensão dos Retimers

A física é implacável. À medida que aumentamos a frequência para 64 GT/s com PAM-4, o sinal elétrico sofre atenuação severa ao viajar pelo cobre. Em uma placa-mãe padrão, o sinal mal consegue viajar alguns centímetros antes de se tornar ruído indesejável.

Isso criou um mercado explosivo para Retimers. Chips especializados, como os da série Aries da Astera Labs (que viu suas ações dispararem após o IPO em 2024), atuam como repetidores inteligentes. Eles capturam o sinal degradado, limpam o ruído, regeneram o sinal e o retransmitem. Sem retimers, o CXL 3.0 não funcionaria fora do encapsulamento da CPU. Eles são os "amplificadores" que permitem que a arquitetura desagregada exista fisicamente, estendendo o alcance do cobre para conectar gavetas de memória e storage dentro do rack.

💡 Dica Pro: Ao projetar infraestrutura para a era CXL, o orçamento de energia e refrigeração deve considerar os retimers. Eles não são passivos; são chips ativos que consomem energia e geram calor. Um backplane CXL denso pode ter dezenas deles.

O horizonte de 2027: Silicon Photonics e o Optical CXL

Se o cobre é o limite atual, a luz é o destino. Para sair do rack e conectar fileiras inteiras de servidores em um único pool de memória (Cluster-Scale), precisaremos abandonar os elétrons.

A Silicon Photonics (Fotônica de Silício) está integrando lasers e detectores diretamente nos chips. Empresas como Ayar Labs e a própria Intel estão desenvolvendo transceptores ópticos que se conectam diretamente ao soquete da CPU ou ao switch CXL. O objetivo é o Optical CXL: latência de nanossegundos a distâncias de metros ou até quilômetros.

Isso permitirá a criação de datacenters onde "o computador" é o prédio inteiro. O armazenamento não estará mais em um servidor, nem mesmo em um SAN tradicional, mas em um "tijolo" de memória persistente acessível via luz por qualquer unidade de processamento no edifício.

Figura: A transição do elétron para o fóton: Interface de Silicon Photonics substituindo pinos de cobre por feixes de luz para comunicação CXL de longa distância.

Figura: A transição do elétron para o fóton: Interface de Silicon Photonics substituindo pinos de cobre por feixes de luz para comunicação CXL de longa distância.

O imperativo da adaptação

Não estamos apenas falando de uma atualização de hardware; estamos falando de uma mudança na filosofia de design de sistemas. O administrador de storage de 2028 não gerenciará LUNs ou volumes em um array isolado. Ele gerenciará espaços de endereçamento globais e tiers de latência em um fabric fluido.

A rigidez do servidor monolítico serviu ao propósito da era da computação pessoal e da virtualização inicial. Mas na era da Inteligência Artificial, onde modelos de linguagem exigem terabytes de memória de acesso rápido, e bancos de dados in-memory crescem exponencialmente, prender a memória em caixas de metal é um luxo que a física e a economia não permitem mais. O hardware está se tornando líquido. Prepare sua infraestrutura para fluir.

Perguntas Frequentes (FAQ)

O CXL 3.0 aumenta a latência da memória em comparação ao DDR5 local?

Minimamente. O CXL adiciona cerca de uma viagem de ida e volta de latência de barramento (aprox. 170-200ns vs 80-100ns do DDR local). No entanto, para a maioria das cargas de trabalho de banco de dados in-memory e IA, essa diferença é negligenciável comparada ao ganho de capacidade e largura de banda, especialmente com as otimizações de FLIT do PCIe 6.0.Posso usar módulos CXL 2.0 em um host CXL 3.0?

Sim. O padrão é totalmente retrocompatível. Um host CXL 3.0 pode se comunicar com dispositivos 2.0 e 1.1, embora a velocidade seja negociada para o menor denominador comum (32 GT/s no caso do CXL 2.0).Qual a diferença entre Expansão de Memória e Pooling de Memória?

Expansão é apenas adicionar mais RAM a um único servidor via slot PCIe. Pooling (introduzido no CXL 2.0 e aprimorado no 3.0) permite que um 'banco' de memória seja compartilhado dinamicamente entre vários servidores, alocando e desalocando capacidade conforme a demanda, sem reiniciar as máquinas.

Julian Vance

Futurista de Tecnologia

"Exploro as fronteiras da infraestrutura, do armazenamento em DNA à computação quântica. Ajudo líderes a decodificar o horizonte tecnológico e construir o datacenter de 2035 hoje."