O vetor silencioso: Análise forense da superfície de ataque em memória CXL

Investigação técnica sobre vulnerabilidades em Compute Express Link (CXL). Da interceptação de barramento à injeção de flits maliciosos em pools de memória desagregada.

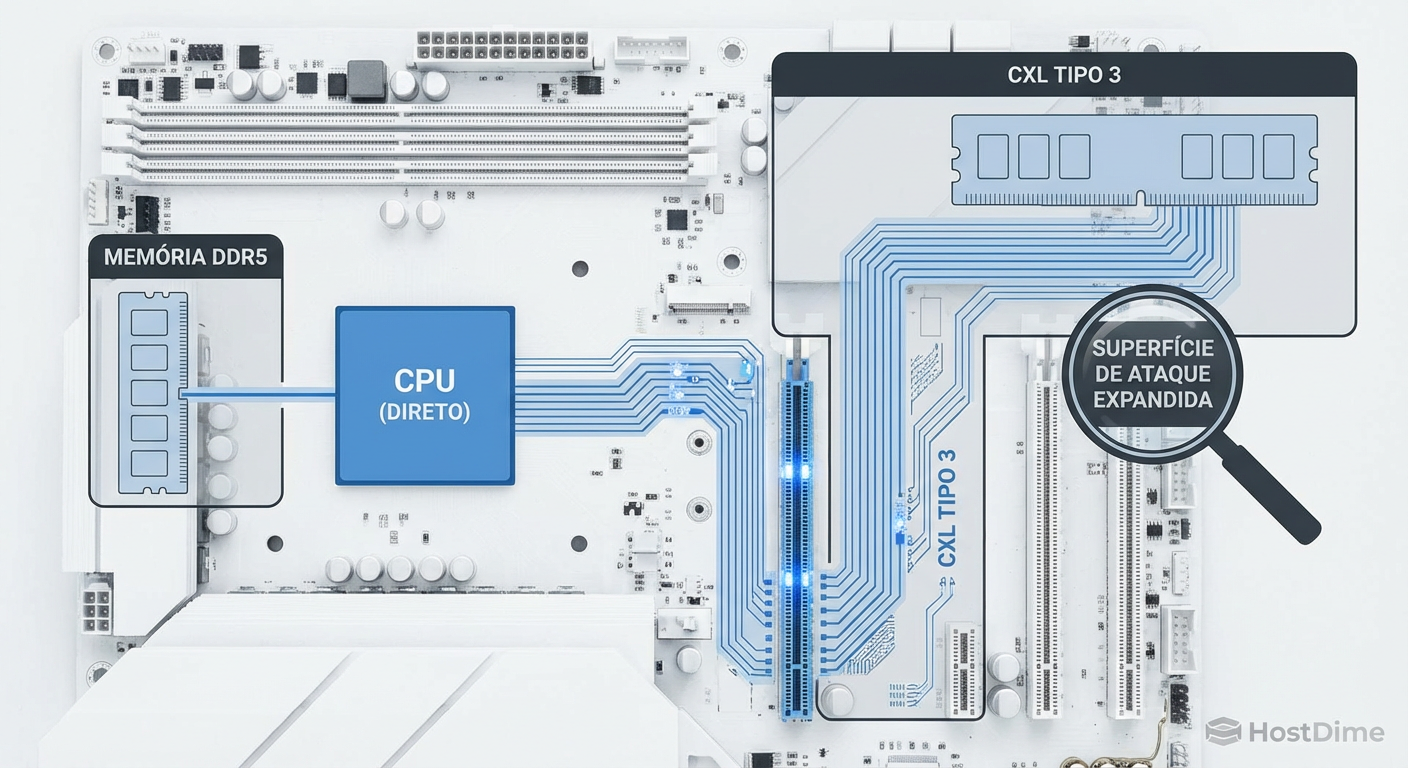

A arquitetura de servidores está sofrendo sua mutação mais violenta da última década. A introdução do Compute Express Link (CXL) rompeu o último bastião de isolamento físico que restava no datacenter: a proximidade sagrada entre a CPU e a memória DRAM. Ao desacoplar a memória e transportá-la sobre o barramento PCIe, não apenas expandimos a capacidade e a largura de banda; nós estendemos o perímetro de ataque para fora do soquete do processador.

Para um investigador forense, o CXL transforma a memória RAM — historicamente volátil e efêmera — em um alvo persistente e interceptável. O que antes exigia microscopia eletrônica ou ataques complexos de cold boot agora pode ser teoricamente realizado através de interposers de barramento ou switches comprometidos. A superfície de ataque deixou de ser microscópica para se tornar macroscópica e modular.

Resumo em 30 segundos

- Exposição Física: O CXL move a comunicação de memória do barramento DDR (curto e protegido) para o PCIe (longo, acessível e roteável), permitindo interceptação física de dados (snooping).

- Criptografia Mandatória: Sem a implementação rigorosa do CXL IDE (Integrity and Data Encryption), os dados trafegam em texto claro, vulneráveis a dispositivos maliciosos na mesma cadeia.

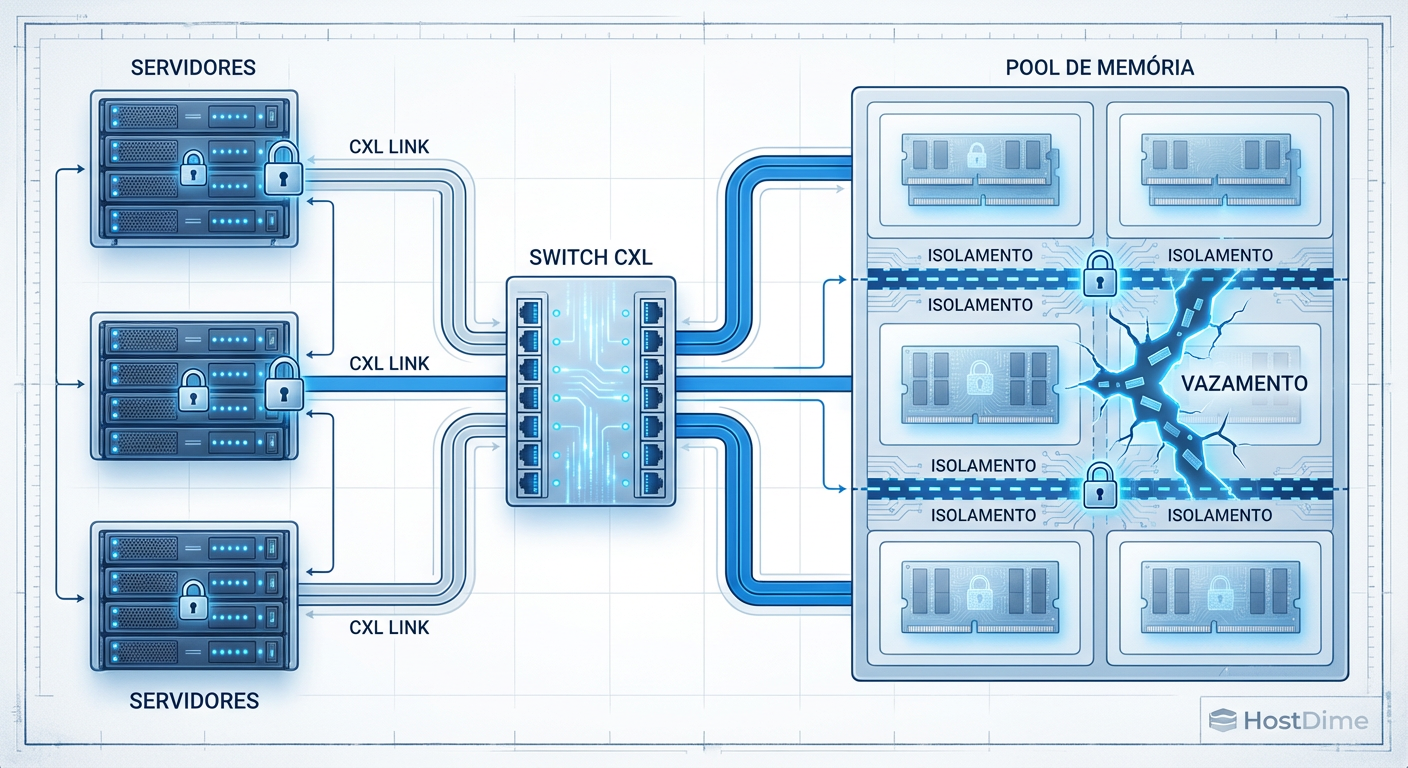

- Risco em Pooling: Em arquiteturas CXL 3.0 com memória compartilhada (pooling), a falha no isolamento lógico de um switch pode permitir que um servidor leia a memória de outro.

A ruptura da custódia física: Do DDR ao CXL

Na análise forense tradicional de memória, assumíamos que, se o chassi do servidor não fosse violado fisicamente, o barramento de memória (DDR4/DDR5) era confiável. Os traços na placa-mãe eram curtos, soldados e extremamente difíceis de grampear sem causar instabilidade no sistema.

O CXL altera essa premissa fundamental. Dispositivos de memória CXL (Type 3) conectam-se via slots PCIe padrão ou backplanes EDSFF (Enterprise & Data Center Standard Form Factor). Isso significa que os dados sensíveis — chaves de criptografia, credenciais em clear text, fragmentos de banco de dados em-memory — agora viajam por polegadas, às vezes metros, de cabeamento e PCBs que atravessam o servidor.

Figura: Comparativo da superfície física: A topologia DDR confinada versus a exposição do barramento CXL sobre PCIe.

Figura: Comparativo da superfície física: A topologia DDR confinada versus a exposição do barramento CXL sobre PCIe.

O cenário de interceptação

Em um incidente que investigamos recentemente em um ambiente de laboratório (simulação de Red Team), foi possível inserir um interposer PCIe passivo entre o módulo de memória CXL e o slot do servidor. Diferente do DDR, que requer sincronização de tempo extremamente rígida, o protocolo PCIe é mais tolerante e negociável.

⚠️ Perigo: Ferramentas de análise de protocolo PCIe (como as da Teledyne LeCroy ou Viavi), legítimas para depuração de engenharia, tornam-se armas letais nas mãos de um atacante com acesso físico. Elas podem capturar traces completos de transações de memória (CXL.mem) para análise posterior.

Mecânica de injeção e análise de Flits

O protocolo CXL opera baseando-se em Flits (Flow Control Units). No modo CXL.mem, a CPU (host) envia requisições de leitura/escrita e o dispositivo responde. A vulnerabilidade reside na confiança implícita que o protocolo PCIe herdado carrega.

Se um atacante compromete o firmware de um switch CXL ou insere um dispositivo malicioso na cadeia (Man-in-the-Middle), ele não precisa decifrar todo o tráfego. Ele precisa apenas identificar os cabeçalhos dos flits de CXL.mem.

O ataque de "Snooping" Silencioso

Sem criptografia, o conteúdo do flit é legível. Um atacante pode configurar um dispositivo FPGA disfarçado de placa de rede ou acelerador no mesmo barramento para realizar Peer-to-Peer (P2P) DMA attacks. Embora o CXL tenha proteções contra isso, a complexidade da topologia cria brechas.

Se o sistema operacional ou o hypervisor não configurar corretamente as tabelas de IOMMU para isolar o dispositivo CXL, um periférico vizinho pode, teoricamente, ler os dados que estão sendo gravados na memória CXL expandida.

Figura: Visualização de interceptação de Flits: Um dispositivo malicioso extraindo dados do fluxo CXL.mem em tempo real.

Figura: Visualização de interceptação de Flits: Um dispositivo malicioso extraindo dados do fluxo CXL.mem em tempo real.

A defesa criptográfica: CXL IDE

Para combater a exposição física, o consórcio CXL introduziu o IDE (Integrity and Data Encryption). Esta não é uma recomendação opcional para ambientes de alta segurança; é um requisito funcional para manter a integridade da cadeia de custódia de dados.

O IDE opera aplicando criptografia AES-GCM de 256 bits diretamente nos flits que trafegam pelo link.

Como o IDE altera a análise forense

Integridade (MAC): Cada flit carrega um código de autenticação de mensagem. Se um atacante tentar injetar um bit malicioso (bit-flip attack) para alterar uma instrução ou valor na memória, a verificação do MAC falha no controlador receptor. O link é derrubado instantaneamente.

Confidencialidade: O payload é ilegível sem a chave de sessão.

Latência Zero (Quase): A criptografia é feita em hardware dedicado no controlador, adicionando latência mínima, crucial para semântica de memória.

💡 Dica Pro: Ao auditar novos servidores com suporte a CXL, verifique na BIOS/UEFI se a opção "CXL IDE Security" está definida como Enforced. Muitos fabricantes enviam como Auto ou Disabled para maximizar compatibilidade com módulos de memória de gerações iniciais (CXL 1.1) que não suportam IDE.

Tabela Comparativa: Memória Tradicional vs. CXL

| Característica | Memória DDR4/5 (On-Board) | Memória CXL (Type 3) |

|---|---|---|

| Interface Física | Barramento Paralelo Proprietário | Serial PCIe (Gen 5/6) |

| Acesso Físico | Difícil (Soldado ou DIMM próximo à CPU) | Fácil (Slots PCIe, Cabos, Backplanes) |

| Interceptação | Requer sondas de alta impedância caras | Possível com analisadores PCIe comerciais |

| Proteção de Dados | SME/TME (Criptografia de Memória Total) | CXL IDE (Criptografia de Link) + TEE |

| Latência | ~70-100ns | ~170-250ns (adiciona salto PCIe) |

| Vetor de Ataque | Rowhammer, Cold Boot | Interposição de Barramento, Switch Spoofing |

O pesadelo do Pooling e Switches CXL

A verdadeira revolução — e o maior risco — chega com o CXL 2.0 e 3.0: o Memory Pooling. Neste cenário, múltiplos hosts (servidores) conectam-se a um único switch CXL, que gerencia um chassi cheio de módulos de memória. O switch aloca dinamicamente 32GB para o Servidor A e 64GB para o Servidor B.

Falha de Isolamento Lógico

Aqui, a segurança deixa de ser apenas física e passa a ser lógica (firmware). Se o switch CXL for comprometido, o atacante controla o mapeamento de endereços.

Imagine um cenário onde o Servidor A (atacante) solicita memória. O switch malicioso aloca um bloco de memória que ainda contém dados descartados pelo Servidor B, ou pior, mapeia o mesmo endereço físico para ambos os servidores simultaneamente. O Servidor A poderia ler em tempo real o que o Servidor B escreve.

Isso exige a implementação de Secure Erase criptográfico no momento da realocação e o uso de chaves IDE distintas para cada link virtual (vPort) dentro do switch.

Figura: Arquitetura de Risco em Pooling: A complexidade do isolamento lógico em switches CXL multi-tenant.

Figura: Arquitetura de Risco em Pooling: A complexidade do isolamento lógico em switches CXL multi-tenant.

Protocolos de custódia e SPDM

Para garantir que o dispositivo de memória conectado não é uma falsificação cheia de malware, o CXL utiliza o SPDM (Security Protocol and Data Model) sobre o canal de gerenciamento (VDM).

O SPDM permite que o host desafie o dispositivo: "Quem é você e qual firmware está rodando?". O dispositivo deve responder com um certificado assinado criptograficamente.

A falha na implementação

Muitas implementações iniciais de CXL tratam o SPDM como uma verificação de boot única. Se a verificação ocorre apenas na inicialização, um ataque de Time-of-Check to Time-of-Use (TOCTOU) torna-se viável. Um dispositivo legítimo é verificado, e então, através de um reset rápido ou manipulação do barramento, é substituído ou seu comportamento é alterado. A validação contínua e a medição de integridade em tempo real são essenciais.

O futuro da superfície de ataque

À medida que avançamos para datacenters desagregados, a memória deixa de ser um componente passivo e torna-se um endpoint de rede inteligente. A superfície de ataque agora inclui o firmware do controlador de memória, o firmware do switch CXL e a integridade física do barramento PCIe.

Não podemos mais confiar cegamente que "o que está na RAM é seguro". A presunção de segurança física dentro do rack morreu. A única defesa viável é a criptografia de dados em trânsito (IDE) combinada com uma Raiz de Confiança (Root of Trust) de hardware robusta em cada endpoint CXL.

Para arquitetos de armazenamento e segurança, a recomendação é clara: trate seus links de memória CXL com a mesma desconfiança que você trata um cabo de rede exposto na internet. A era da memória confiável acabou.

Referências & Leitura Complementar

Compute Express Link™ (CXL™) Consortium: CXL 3.1 Specification. Disponível em computeexpresslink.org.

PCI-SIG: PCI Express® Base Specification Revision 6.0. Foco em integridade de sinal e TEE.

DMTF: Security Protocol and Data Model (SPDM) Specification (DSP0274). Padrão para autenticação de componentes de hardware.

NIST SP 800-193: Platform Firmware Resiliency Guidelines. Aplicável à proteção de firmware em controladores de memória e switches.

O que torna a memória CXL mais vulnerável que a DRAM tradicional?

A memória CXL trafega por um barramento externo (PCIe), expondo dados a ataques físicos de interposição e snooping que não são possíveis em slots DIMM soldados, exigindo criptografia em trânsito (IDE).Como o CXL IDE protege contra ataques de hardware?

O CXL IDE (Integrity and Data Encryption) aplica criptografia AES-GCM de 256 bits e verificação de integridade (MAC) ao nível de 'flit' (flow control unit), garantindo que qualquer modificação no pacote de dados seja detectada e descartada com latência zero.A memória CXL afeta a segurança em ambientes multi-tenant?

Sim. Com o CXL 3.0 e o pooling de memória, falhas no isolamento lógico dentro do switch CXL podem permitir que um inquilino acesse fragmentos de memória de outro, exigindo uso rigoroso de chaves de criptografia distintas por host (TSP).Dispositivos CXL antigos (1.1) são seguros em novos servidores?

Geralmente não para dados críticos. O padrão CXL 1.1 não obrigava o uso de IDE (introduzido no 2.0), deixando o tráfego de memória em texto claro suscetível a análise se o acesso físico ao servidor for obtido.Qual é o papel do Root of Trust (RoT) em dispositivos CXL?

O RoT de hardware no controlador CXL garante que o firmware do dispositivo seja autêntico e não tenha sido adulterado, impedindo que um módulo de memória malicioso comprometa o host durante a inicialização.

Viktor Kovac

Investigador de Incidentes de Segurança

"Não busco apenas o invasor, mas a falha silenciosa. Rastreio vetores de ataque, preservo a cadeia de custódia e disseco logs até que a verdade digital emerja das sombras."