PCIe 5.0 e a instabilidade silenciosa: dissecando falhas em retimers NVMe

Análise forense da integridade de sinal em 32 GT/s. Descubra como retimers mal implementados causam latência fantasma e quedas de link em backplanes de alta densidade.

A velocidade tem um preço e, no ecossistema de armazenamento moderno, a moeda de troca é a estabilidade do sinal. Quando a indústria dobrou a taxa de transferência de 16 GT/s (Gen4) para 32 GT/s (Gen5), não apenas aumentamos a largura de banda; nós efetivamente transformamos o design de placas-mãe e backplanes em um pesadelo de radiofrequência.

Para o engenheiro de infraestrutura que observa um array de SSDs NVMe Enterprise desaparecer aleatoriamente do sistema operacional, a causa raiz raramente é o disco em si. O verdadeiro culpado reside na "milha intermediária" entre a CPU e o armazenamento: os retimers e a física impiedosa da integridade de sinal. Se você acha que o PCIe 5.0 é apenas "plug-and-play" mais rápido, prepare-se para ver seus logs de erro sangrarem.

Resumo em 30 segundos

- Física Hostil: Em 32 GT/s, a perda de sinal na PCB é tão agressiva que traços de cobre comuns agem como filtros passa-baixa, destruindo dados em distâncias curtas.

- Redriver vs. Retimer: A amplificação simples (Redriver) não funciona mais de forma confiável no Enterprise; é necessário regenerar o sinal completamente (Retimer), o que introduz latência e calor.

- Falha LTSSM: A maioria dos "discos mortos" são, na verdade, falhas na negociação de link (LTSSM) causadas por instabilidade térmica ou elétrica nos retimers.

A física impiedosa da perda de inserção em 32 GT/s

No mundo do armazenamento de alta performance, a ignorância sobre a camada física é uma sentença de morte para a disponibilidade. O sinal PCIe 5.0 opera com uma frequência de Nyquist de 16 GHz. Nessa frequência, a placa de circuito impresso (PCB) deixa de ser um condutor passivo e se torna um componente ativo e hostil.

O fenômeno crítico aqui é a Perda de Inserção (Insertion Loss). Materiais padrão como o FR4, que serviram bem até o PCIe 3.0, agora agem como esponjas absorvendo a energia do sinal. Além disso, temos o efeito pelicular (skin effect), onde a corrente flui apenas na superfície externa do condutor, aumentando drasticamente a resistência.

💡 Dica Pro: Em designs de servidores Gen5, a perda aceitável é de aproximadamente -36dB. Sem chips auxiliares, o sinal elétrico de um slot PCIe 5.0 morre após percorrer cerca de 10 a 15 centímetros de trilha na placa-mãe. Se o seu backplane de storage está longe da CPU, você está operando no escuro.

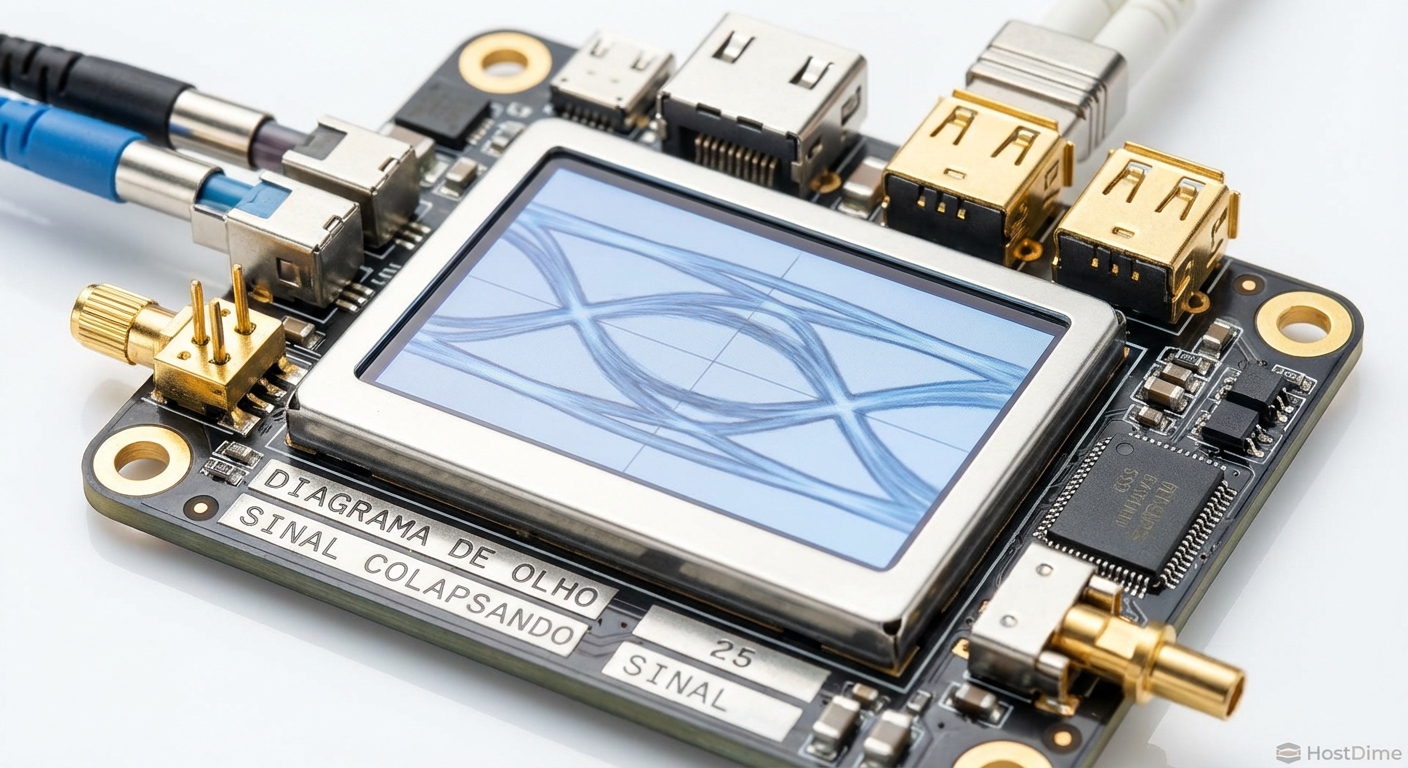

Figura: Visualização técnica de um diagrama de olho (eye diagram) do sinal PCIe 5.0 colapsando devido à perda de inserção e ruído.

Figura: Visualização técnica de um diagrama de olho (eye diagram) do sinal PCIe 5.0 colapsando devido à perda de inserção e ruído.

Quando o sinal degrada, o receptor no SSD NVMe não consegue distinguir um bit '1' de um '0'. Isso não gera apenas um erro de leitura; gera um colapso na negociação do link, forçando o sistema a tentar recuperar a conexão, muitas vezes sem sucesso.

Por que a amplificação analógica cega falha no enterprise

Historicamente, para estender o alcance do sinal, usávamos Redrivers. Eles são amplificadores analógicos simples. Pense neles como alguém gritando uma mensagem para outra pessoa em uma sala barulhenta. O Redriver aumenta o volume da voz, mas também aumenta o volume do ruído de fundo.

No PCIe 4.0, isso era aceitável. No PCIe 5.0, a margem de ruído é tão estreita que amplificar o ruído junto com o sinal destrói a integridade dos dados. É aqui que entram os Retimers.

Um Retimer não apenas amplifica. Ele captura o sinal, decodifica-o, verifica erros, regenera uma cópia limpa e a retransmite com a temporização (clock) corrigida. Ele é um "repetidor inteligente" que participa ativamente do protocolo. No entanto, essa inteligência tem um custo térmico e de complexidade que muitos arquitetos de storage subestimam.

Comparativo: Redriver vs. Retimer em Storage Gen5

| Característica | Redriver (Amplificador Linear) | Retimer (Regenerador de Sinal) |

|---|---|---|

| Função Principal | Amplificação analógica cega (Sinal + Ruído) | Recuperação de Dados e Relógio (CDR) |

| Visibilidade no OS | Invisível (Transparente) | Visível (Possui endereçamento no barramento) |

| Reset de Jitter | Não (Propaga o jitter) | Sim (Reseta o budget de jitter) |

| Consumo de Energia | Baixo | Alto (Ponto quente crítico na PCB) |

| Custo | Baixo | Alto (Complexidade de silício) |

| Uso em Gen5 | Apenas traços muito curtos (<5 pol) | Obrigatório para Backplanes e Cabos Riser |

O colapso da máquina de estados LTSSM sob estresse

A parte mais fascinante e destrutiva de um sistema de storage moderno é a LTSSM (Link Training and Status State Machine). É o cérebro que gerencia a conexão PCIe. Quando você espeta um SSD NVMe, a LTSSM passa por estados como Detect, Polling, Configuration e L0 (estado ativo).

Em cenários de caos, onde introduzimos calor excessivo ou flutuação de tensão, os retimers Gen5 frequentemente falham em manter a equalização correta. O resultado? O link cai do estado L0 para Recovery.

Se a recuperação falhar repetidamente, a LTSSM pode decidir, em uma tentativa desesperada de sobrevivência, renegociar o link para uma velocidade menor (downgrade para Gen4 ou Gen3) ou reduzir a largura do link (de x4 para x2 ou x1).

⚠️ Perigo: Um SSD NVMe operando em x1 Gen3 devido a falha de retimer não aciona necessariamente um alerta de "disco falho" em todos os controladores RAID ou SDS (Software Defined Storage). O disco continua lá, mas sua latência dispara de 80µs para milissegundos, criando uma "latência de cauda" que pode derrubar a performance de todo o cluster vSAN ou Ceph.

O fator térmico nos Retimers

Retimers PCIe 5.0 são pequenos fornos. Um chip retimer de 16 pistas (lanes) pode dissipar entre 8W a 12W. Em um servidor 1U denso, com fluxo de ar restrito pelos próprios discos que ele serve, o retimer pode entrar em thermal throttling.

Quando o retimer superaquece, ele começa a introduzir erros de bit (BER - Bit Error Rate). O protocolo PCIe tenta corrigir com CRC, mas se a taxa de erro exceder a capacidade de replay, o link cai.

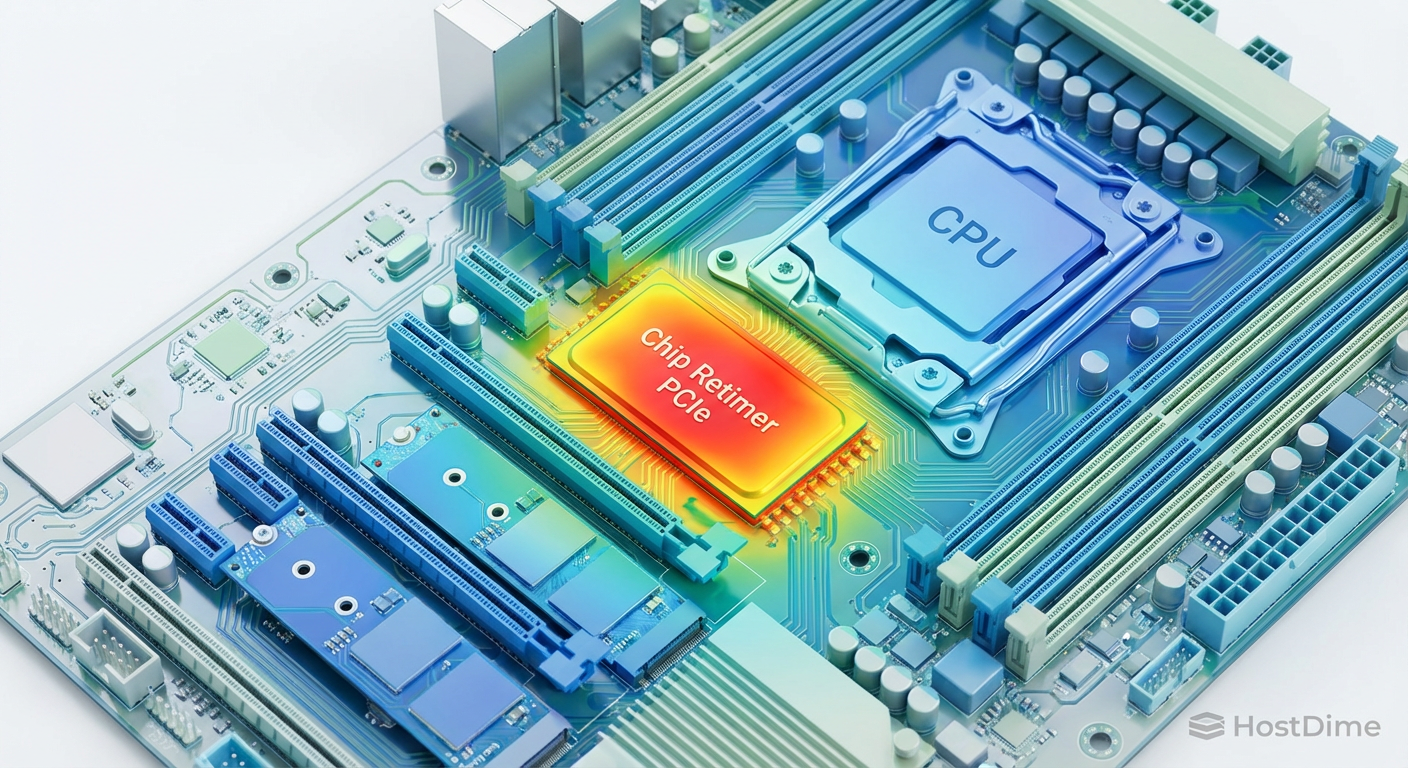

Figura: Mapa de calor (imagem térmica) de uma placa-mãe de servidor destacando um chip retimer PCIe extremamente quente localizado entre a CPU e os conectores NVMe.

Figura: Mapa de calor (imagem térmica) de uma placa-mãe de servidor destacando um chip retimer PCIe extremamente quente localizado entre a CPU e os conectores NVMe.

Implementando topologias resilientes

Para sobreviver ao caos do PCIe 5.0, a engenharia de storage teve que evoluir. Não basta mais desenhar trilhas na placa. Estamos vendo uma mudança massiva para o uso de cabeamento over-the-board e materiais exóticos.

Materiais de Baixa Perda: O uso de laminados como Megtron 6 ou Tachyon 100G é obrigatório para reduzir a perda dielétrica. O FR4 comum é radioativamente ruim para Gen5.

Cabeamento MCIO e DAC: Em vez de passar o sinal pela PCB da placa-mãe, os designs modernos usam cabos MCIO (Mini Cool Edge IO) que saem direto perto da CPU e voam até o backplane dos discos. O cabo coaxial ou twinax tem perda de inserção muito menor que a PCB.

Bifurcação e Isolamento: Retimers modernos permitem segmentar as pistas. Se um SSD causa ruído excessivo na linha, um retimer inteligente pode isolar aquelas 4 pistas sem derrubar as outras 12 que passam pelo mesmo chip.

Protocolos de isolamento e renegociação sem reboot

A resiliência real vem da capacidade de recuperar o sistema sem intervenção humana (e sem reboot). No contexto de storage de missão crítica, o recurso de Hot Plug depende inteiramente da capacidade do retimer de detectar a presença e iniciar a LTSSM limpa.

Um cenário de teste de caos que executamos frequentemente envolve a injeção de erros na camada física para forçar o retimer a recalibrar seus filtros (CTLE/DFE). Um sistema robusto deve ser capaz de realizar um Link Retraining em menos de 100ms. Se o firmware do retimer for mal otimizado, esse processo pode levar segundos, causando timeout no driver NVMe do sistema operacional e resultando em I/O error para a aplicação.

A "renegociação sem reboot" é o Santo Graal. Se um link degrada por temperatura, o sistema deve baixar a velocidade para Gen4 dinamicamente e, assim que a temperatura estabilizar, tentar subir para Gen5 novamente. Infelizmente, muitos firmwares de SSDs e Retimers atuais preferem morrer (link down) a negociar (speed downgrade).

O futuro é ainda mais ruidoso

Estamos caminhando para um cenário onde a integridade do sinal é o principal gargalo de performance em storage. Com a chegada iminente do PCIe 6.0 e sua modulação PAM4 (que é ainda mais sensível a ruído que o NRZ do Gen5), a dependência de retimers e DSPs (Processamento Digital de Sinal) será total.

Para o engenheiro de storage hoje, a lição é clara: pare de confiar cegamente na especificação de velocidade da caixa. Valide a topologia, monitore a temperatura dos retimers (não apenas da CPU e dos Discos) e prepare sua arquitetura de software para lidar com links que flutuam, mentem e desaparecem. A estabilidade não é dada; ela é forjada no fogo do estresse contínuo.

Referências & Leitura Complementar

PCI-SIG: PCI Express Base Specification Revision 5.0. (Documentação oficial do padrão).

Astera Labs: Cloud-Scale Interconnects for the Data Centric Era. (Whitepapers sobre a arquitetura de Smart Retimers Aries).

Microchip Technology: XpressConnect Retimers Datasheets. (Detalhes técnicos sobre latência e modos de operação de retimers).

OCP (Open Compute Project): Datacenter NVMe SSD Specification. (Especificações sobre requisitos térmicos e de sinal para SSDs em escala).

Qual a diferença crítica entre Redriver e Retimer no PCIe 5.0?

O Redriver apenas amplifica o sinal (com ruído), atuando como um megafone analógico. O Retimer regenera o sinal criando uma cópia limpa, reseta o jitter e participa ativamente do protocolo PCIe, sendo indispensável para distâncias longas em Gen5.Por que meus SSDs NVMe Gen5 desaparecem aleatoriamente do sistema?

Geralmente devido a falhas na negociação do link (LTSSM) causadas por superaquecimento do retimer ou degradação do sinal além da capacidade de correção de erros. O link cai e o drive é removido logicamente pelo OS.O que é perda de inserção em backplanes de storage?

É a redução da potência do sinal à medida que ele viaja pela PCB ou cabo. No PCIe 5.0 (32 GT/s), essa perda é drástica devido à alta frequência, exigindo chips auxiliares (retimers) para distâncias acima de alguns centímetros.

Magnus Vance

Engenheiro do Caos

"Quebro sistemas propositalmente porque a falha é inevitável. Transformo desastres simulados em vacinas para sua infraestrutura. Se não sobrevive ao meu caos, não merece estar em produção."