PCIe 6.0 e o paradoxo do PAM4: quando a largura de banda ameaça a latência do NVMe

Análise profunda sobre como a modulação PAM4 no PCIe 6.0 dobra a velocidade para 64 GT/s, mas introduz latência via FEC, desafiando a performance de SSDs NVMe.

A evolução da infraestrutura de dados atingiu um ponto de inflexão que raramente vemos na história da computação. Durante décadas, a indústria confiou em um aumento linear de frequência para ganhar velocidade. Mas com a chegada do PCIe 6.0, as leis da física impuseram um ultimato aos engenheiros de hardware: a velocidade bruta não é mais suficiente se o sinal se degradar em ruído antes de chegar ao controlador do SSD. Estamos entrando na era da modulação complexa dentro do barramento, uma mudança que altera fundamentalmente como os dados trafegam entre a CPU e o armazenamento.

Resumo em 30 segundos

- Mudança de Paradigma: O PCIe 6.0 abandona a sinalização binária simples (NRZ) em favor do PAM4, que transmite 2 bits por ciclo usando quatro níveis de voltagem, dobrando a largura de banda para 64 GT/s.

- O Custo da Latência: A complexidade do PAM4 aumenta a taxa de erros de bits. Para corrigir isso, o uso de FEC (Forward Error Correction) torna-se obrigatório, adicionando uma penalidade de latência que afeta diretamente SSDs de alta performance.

- Solução via FLIT: Para compensar o atraso do FEC, o PCIe 6.0 introduz o modo FLIT (Flow Control Unit), eliminando a sobrecarga de codificação antiga e permitindo que a latência permaneça competitiva para cargas de trabalho críticas.

O fim da era binária e a morte do NRZ

Até a geração 5.0, o padrão PCI Express operava sob uma premissa reconfortante e simples: a sinalização NRZ (Non-Return-to-Zero). Neste modelo, a voltagem alta representava um "1" e a voltagem baixa representava um "0". Era um sistema robusto. O "olho" do sinal — a representação gráfica da distinção entre os dois estados — era bem aberto, permitindo que os controladores de armazenamento lessem os dados com facilidade, mesmo com alguma interferência elétrica.

No entanto, para alcançar os 64 GT/s (Gigatransfers por segundo) exigidos pelo PCIe 6.0, manter o NRZ exigiria dobrar a frequência do barramento para níveis insustentáveis em placas de circuito padrão (PCB) de material FR4. A perda de sinal (insertion loss) transformaria os traços de cobre da placa-mãe em antenas inúteis, dissipando dados antes que chegassem ao drive NVMe.

A solução foi a adoção do PAM4 (Pulse Amplitude Modulation 4-level). Em vez de dois níveis de voltagem, o PAM4 utiliza quatro. Isso permite codificar dois bits (00, 01, 10, 11) em um único ciclo de clock. É uma técnica emprestada das redes Ethernet de ultra-velocidade, agora aplicada diretamente no coração da comunicação do servidor.

Figura: Comparativo técnico entre os diagramas de olho do NRZ (esquerda) e PAM4 (direita), ilustrando como a margem de erro diminui drasticamente na nova modulação.

Figura: Comparativo técnico entre os diagramas de olho do NRZ (esquerda) e PAM4 (direita), ilustrando como a margem de erro diminui drasticamente na nova modulação.

A fragilidade do sinal e a necessidade de correção

A transição para o PAM4 traz um efeito colateral imediato: a fragilidade. Como agora temos três "olhos" empilhados verticalmente no mesmo espaço de voltagem que antes ocupava apenas um, a margem de ruído é reduzida drasticamente. Qualquer flutuação menor na energia ou interferência eletromagnética (EMI) pode fazer com que um "10" seja lido incorretamente como um "11".

Para o ecossistema de storage, onde a integridade dos dados é inegociável, isso apresenta um problema crítico. A taxa de erro de bit (BER - Bit Error Rate) bruta do PAM4 é ordens de magnitude pior do que a do NRZ. Sem intervenção, os dados chegariam corrompidos ao controlador do SSD.

⚠️ Perigo: Em sistemas PCIe 6.0, a integridade do sinal é tão volátil que a distância física entre a CPU e o SSD se torna um gargalo. O uso de retimers (chips que regeneram o sinal) será praticamente obrigatório em qualquer topologia que não seja conexão direta, aumentando o custo e a complexidade térmica do chassi.

O paradoxo da latência: FEC e o custo do tempo

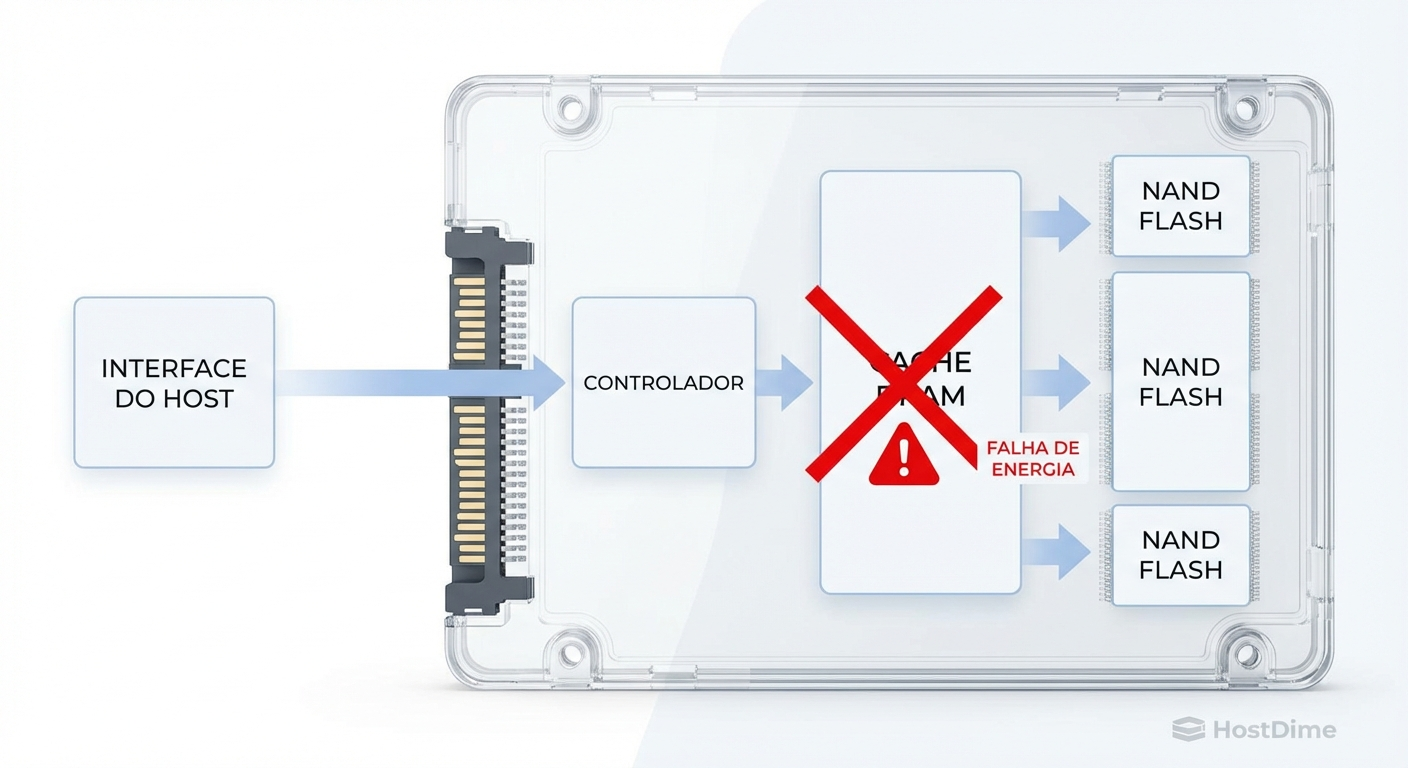

Aqui reside o paradoxo central desta geração. Para mitigar a alta taxa de erros do PAM4, o PCIe 6.0 implementa obrigatoriamente o FEC (Forward Error Correction) de baixa latência. O FEC é um algoritmo matemático que adiciona bits de paridade aos dados transmitidos, permitindo que o receptor (o controlador do SSD) detecte e corrija erros sem precisar pedir o reenvio do pacote.

O problema é que calcular essa correção leva tempo. Em um mundo de discos rígidos mecânicos (HDD), nanossegundos não importam. Mas em um cenário de SSDs NVMe modernos e memórias de classe de armazenamento (como as baseadas em tecnologias persistentes), adicionar latência ao caminho de dados é um pecado capital.

O FEC introduz uma penalidade de latência fixa. O controlador precisa receber o pacote inteiro, processar a matemática de correção e só então liberar os dados para a camada de aplicação. Se não fosse mitigado, isso poderia fazer com que um SSD PCIe 6.0 tivesse um tempo de resposta inicial pior do que um drive PCIe 5.0, apesar de ter o dobro da largura de banda teórica.

Tabela comparativa: O salto geracional

Para visualizar o impacto dessas mudanças na arquitetura de armazenamento, observe as diferenças fundamentais entre as gerações atuais e a nova fronteira:

| Característica | PCIe 4.0 | PCIe 5.0 | PCIe 6.0 |

|---|---|---|---|

| Taxa de Transferência | 16 GT/s | 32 GT/s | 64 GT/s |

| Codificação | NRZ (128b/130b) | NRZ (128b/130b) | PAM4 (1b/1b) |

| Correção de Erro (FEC) | Não Obrigatório | Não Obrigatório | Obrigatório (Leve) |

| Modo de Pacote | TLP/DLLP Variável | TLP/DLLP Variável | FLIT (Tamanho Fixo) |

| Latência Adicional | Baixa | Baixa | Média (Mitigada por FLIT) |

| Foco Principal | Consumer/Enterprise | Enterprise/AI | Hyperscale/HPC |

A salvação via FLIT: Reengenharia de fluxo

Para evitar que o FEC destruísse a proposta de valor de baixa latência do NVMe, o consórcio PCI-SIG introduziu uma mudança radical na camada de protocolo: o modo FLIT (Flow Control Unit).

Nas gerações anteriores, o overhead de codificação (128b/130b) consumia uma pequena parte da banda e o gerenciamento de pacotes era variável. O PCIe 6.0 descarta isso em favor de FLITs de tamanho fixo (256 bytes).

O funcionamento do FLIT é a chave para neutralizar a latência do FEC. Como o tamanho do pacote é conhecido e fixo, o controlador do SSD pode processar os dados de forma muito mais previsível. Além disso, a eficiência da codificação sobe. Não há mais os bits de "framing" do esquema 128b/130b. O FLIT permite que a correção de erro aconteça dentro do fluxo de dados de maneira pipeline, garantindo que a latência total (incluindo o FEC) permaneça abaixo de 10 nanossegundos em implementações ideais.

Isso significa que, embora o processamento seja mais pesado, a eficiência do transporte compensa o atraso matemático. Para o usuário final ou administrador de datacenter, o resultado é transparente: o dobro da velocidade, com latência comparável ou ligeiramente melhor que a geração anterior.

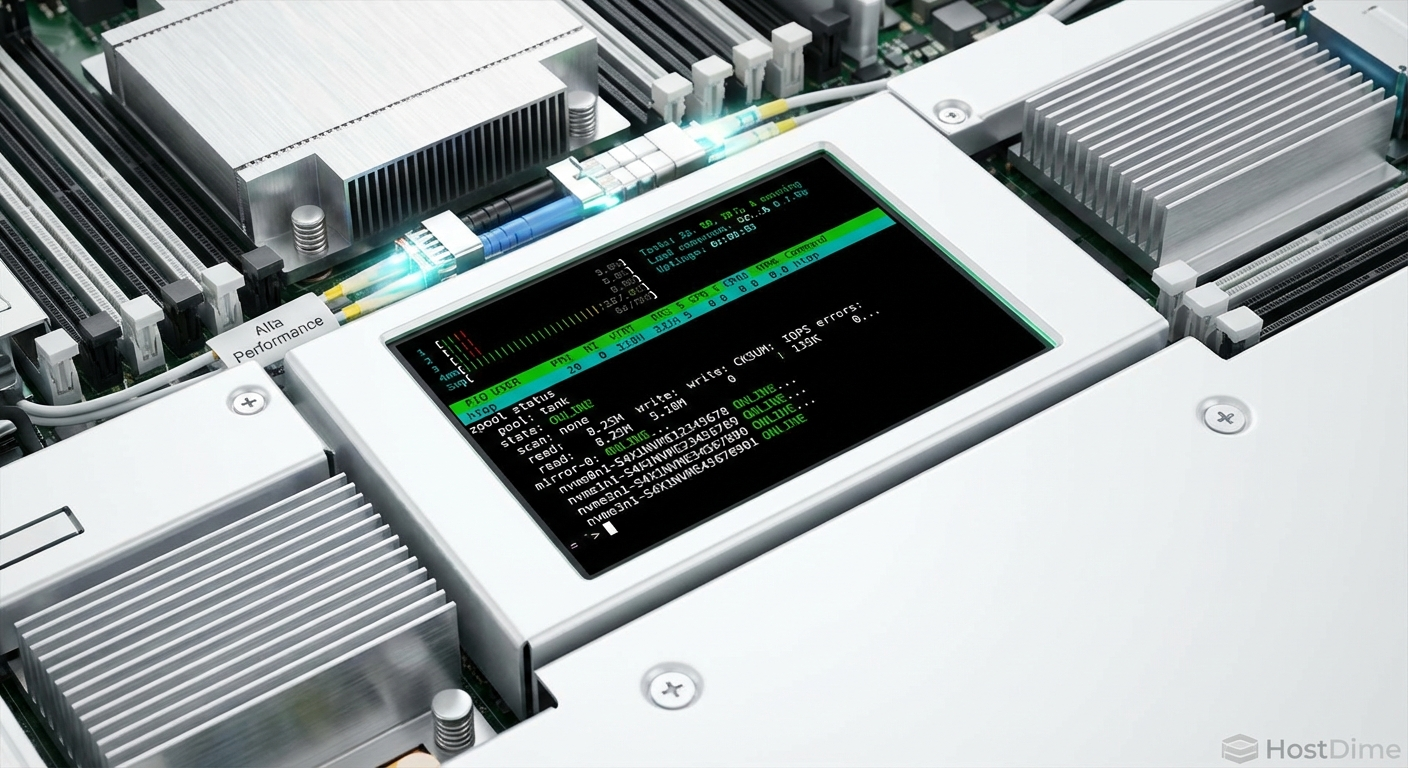

Figura: Visualização abstrata do fluxo de dados em modo FLIT: blocos retangulares de tamanho fixo viajando em alta velocidade por um circuito, com mecanismos internos de autocorreção (FEC) reparando dados em tempo real antes de atingir o controlador NVMe.

Figura: Visualização abstrata do fluxo de dados em modo FLIT: blocos retangulares de tamanho fixo viajando em alta velocidade por um circuito, com mecanismos internos de autocorreção (FEC) reparando dados em tempo real antes de atingir o controlador NVMe.

O limite físico do cobre e a ascensão da fotônica

Olhando para o horizonte de 5 a 10 anos, o PCIe 6.0 é provavelmente o último "grande suspiro" do cobre em longas distâncias dentro do data center sem custos proibitivos. Já estamos vendo a necessidade de cabos ativos (AEC) e redrivers apenas para cruzar o chassi de um servidor 2U.

À medida que nos preparamos para o PCIe 7.0 (128 GT/s), a física dos materiais condutores tradicionais se torna o maior inimigo. A resistência elétrica e o efeito pelicular (skin effect) tornam a transmissão de sinais PAM4 em frequências ainda mais altas uma tarefa hercúlea.

💡 Dica Pro: Ao planejar infraestruturas futuras baseadas em PCIe 6.0 e CXL (Compute Express Link), priorize chassis que suportem backplanes cabeados (cabled backplanes) em vez de trilhas na PCB. A integridade do sinal via cabos twinax internos é superior à das trilhas de fibra de vidro tradicionais.

A tendência inevitável é a integração da fotônica de silício (Silicon Photonics). Em breve, o controlador de armazenamento não receberá mais elétrons através de um slot PCIe de plástico, mas sim fótons através de guias de onda ópticos integrados diretamente ao substrato do processador ou via interconexões ópticas co-empacotadas (CPO - Co-Packaged Optics). O PCIe 6.0 prepara o terreno lógico (com FLIT e FEC) para essa transição física, onde a luz substituirá o cobre para sustentar a largura de banda que a Inteligência Artificial e o Big Data exigem.

Preparando-se para a nova arquitetura

A chegada do PCIe 6.0 e da modulação PAM4 não é apenas uma atualização de velocidade; é um aviso de que a simplicidade da transmissão de dados acabou. Para arquitetos de soluções e entusiastas de hardware, o foco deve mudar da simples leitura de especificações de "MB/s" para a compreensão da topologia do sistema. A qualidade dos cabos, o design da placa-mãe e a eficiência térmica dos controladores NVMe (que agora processam algoritmos complexos de correção de erro) serão os novos diferenciais de performance. Estamos saindo da era da força bruta para a era da precisão algorítmica.

Perguntas Frequentes (FAQ)

O que muda do NRZ para o PAM4 no PCIe 6.0?

Enquanto o padrão antigo NRZ usava apenas dois níveis de voltagem (0 e 1) para transmitir 1 bit por ciclo, o PAM4 introduz quatro níveis distintos de voltagem. Isso permite transmitir 2 bits por ciclo (00, 01, 10, 11), dobrando efetivamente a largura de banda, mas tornando o sinal muito mais sensível a ruídos elétricos.Por que o FEC aumenta a latência em SSDs NVMe?

O Forward Error Correction (FEC) é um cálculo matemático necessário para corrigir os erros frequentes causados pela fragilidade do sinal PAM4. Esse cálculo exige que o controlador do SSD processe os dados antes de aceitá-los, adicionando alguns nanossegundos de atraso (latência) que não existiam nas gerações anteriores sem FEC obrigatório.O PCIe 6.0 é compatível com SSDs PCIe 4.0 e 5.0?

Sim, a retrocompatibilidade é total. No entanto, quando você conecta um SSD antigo (Gen 4 ou 5) em um slot Gen 6, o sistema reverte automaticamente para a sinalização NRZ e opera nas velocidades originais do dispositivo, sem utilizar o PAM4 ou sofrer as penalidades de latência do FEC.

Julian Vance

Futurista de Tecnologia

"Exploro as fronteiras da infraestrutura, do armazenamento em DNA à computação quântica. Ajudo líderes a decodificar o horizonte tecnológico e construir o datacenter de 2035 hoje."