PCIe Gen5 no Data Center: Análise de TCO, Gargalos de I/O e Decisão Arquitetural

O PCIe Gen5 justifica o investimento? Uma análise técnica de arquiteto sobre ROI e performance para workloads de IA, Bancos de Dados e Storage de alta densidade.

Em arquitetura de software e infraestrutura, a resposta padrão para "devemos migrar para a nova tecnologia?" é quase sempre: depende.

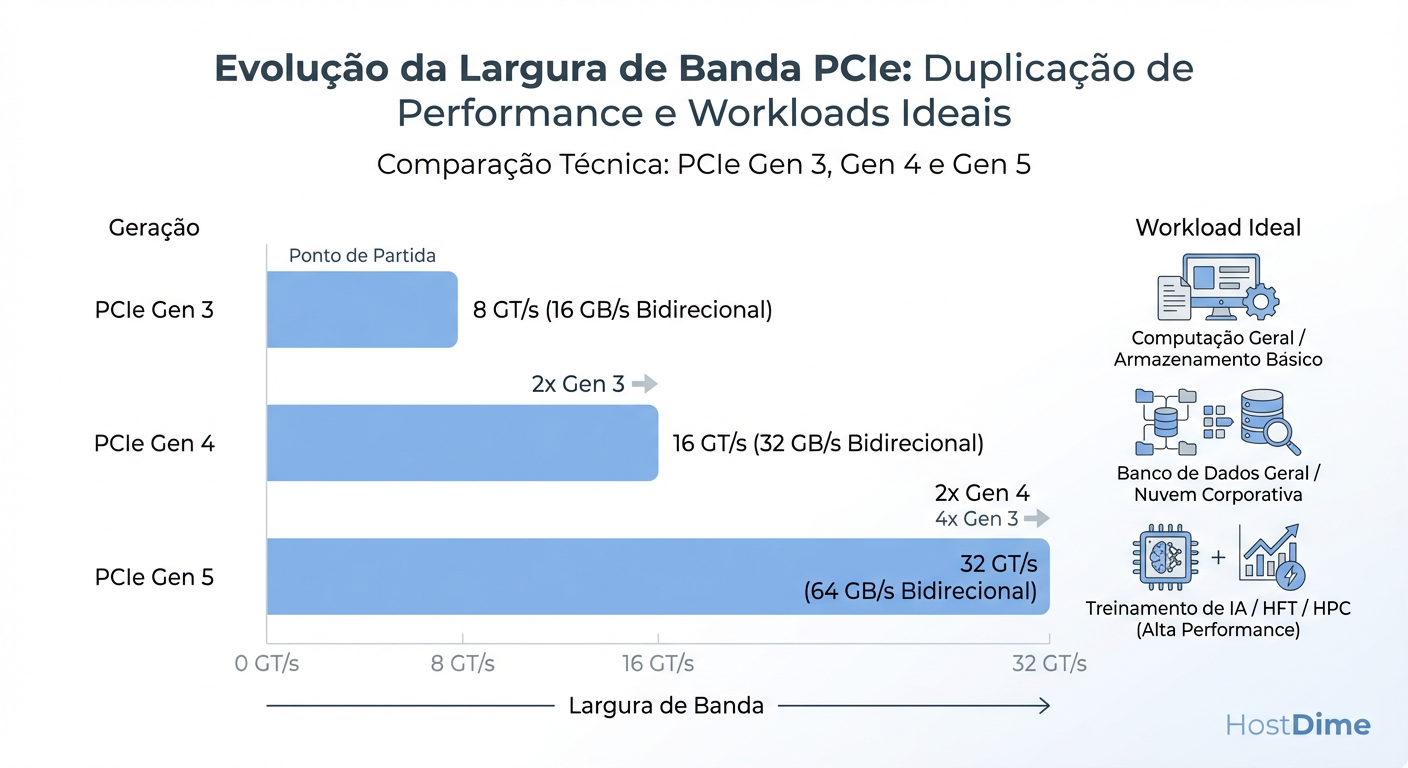

A chegada do PCI Express 5.0 (PCIe Gen5) aos data centers não é exceção. Embora o marketing da indústria foque no dobro da largura de banda teórica (32 GT/s por lane), para um Arquiteto de Soluções Enterprise, a conversa deve girar em torno de eficiência, gargalos de I/O e Custo Total de Propriedade (TCO). Não se trata apenas de velocidade; trata-se de equilibrar a equação econômica da computação de alto desempenho.

A atualização para uma nova geração de barramento não é um exercício trivial de plug-and-play. Ela exige uma reavaliação completa do design do servidor, da densidade térmica e da topologia de interconexão. Neste artigo, analisaremos se o seu workload justifica o prêmio de custo do Gen5 ou se a permanência no Gen4 ainda representa a escolha arquitetural mais prudente.

O Problema de Negócio: Quando o I/O se torna o vilão da performance

Historicamente, a Lei de Moore impulsionou a densidade de transistores e a performance das CPUs, mas a evolução do subsistema de I/O nem sempre acompanhou esse ritmo na mesma proporção. No cenário atual de data centers, enfrentamos o que chamo de "Crise de Alimentação da CPU".

Temos processadores modernos (como AMD EPYC Genoa ou Intel Sapphire Rapids) com contagens massivas de núcleos. No entanto, um núcleo de CPU ocioso, esperando por dados, é o pior tipo de desperdício de CapEx (Capital Expenditure). O problema de negócio fundamental não é a falta de poder de processamento, mas a latência e a largura de banda necessárias para manter esses núcleos saturados.

Onde o gargalo se manifesta:

Workloads de AI/ML: O treinamento de modelos de linguagem (LLMs) exige uma movimentação massiva de tensores entre a VRAM da GPU e a memória do sistema. O barramento PCIe é frequentemente o "tubo" mais estreito.

Storage de Alta Performance: Com o advento dos SSDs NVMe modernos, um único drive pode saturar múltiplas lanes de PCIe Gen3 ou Gen4. Em arrays de armazenamento densos, o barramento se torna o limitador antes mesmo da CPU atingir 50% de uso.

Networking de 400GbE/800GbE: Placas de rede (SmartNICs e DPUs) modernas operando nessas velocidades exigem slots x16 Gen5 completos apenas para não descartar pacotes (packet drop) por falta de vazão no barramento.

Se o seu workload é limitado por computação (CPU-bound), o Gen5 é irrelevante. Se ele é limitado por I/O (I/O-bound), ignorar o Gen5 pode significar dobrar o número de servidores necessários para atingir o mesmo throughput, destruindo seu TCO.

Figura: Fig. 1: A evolução da largura de banda e o mapeamento de workloads ideais por geração.

Figura: Fig. 1: A evolução da largura de banda e o mapeamento de workloads ideais por geração.

Opções Arquiteturais: Comparativo Técnico Gen4 vs. Gen5 e o papel do CXL

Ao desenhar a solução, precisamos comparar o que está na mesa. A transição do Gen4 para o Gen5 mantém a codificação NRZ (Non-Return-to-Zero), mas dobra a frequência de 16 GHz para 32 GHz. Isso é diferente do salto futuro para o Gen6, que utilizará PAM4.

Manter o NRZ simplifica a lógica, mas a 32 GT/s, a física dos materiais se torna impiedosa. A perda de sinal (insertion loss) aumenta drasticamente, o que nos leva a opções arquiteturais distintas.

Tabela Comparativa: Gen4 vs. Gen5

| Característica | PCIe Gen4 | PCIe Gen5 | Impacto Arquitetural |

|---|---|---|---|

| Raw Bit Rate | 16 GT/s | 32 GT/s | Dobro de throughput por lane. |

| Throughput x16 | ~32 GB/s | ~64 GB/s | Permite NICs de 400GbE em um único slot. |

| Codificação | 128b/130b | 128b/130b | Overhead similar (<2%). |

| Alcance do Sinal | ~20 polegadas | ~10-12 polegadas | Exige retimers para distâncias maiores na placa-mãe. |

| Orçamento de Perda | -28 dB | -36 dB | Materiais de PCB mais caros (Low Loss). |

O "Game Changer": Compute Express Link (CXL)

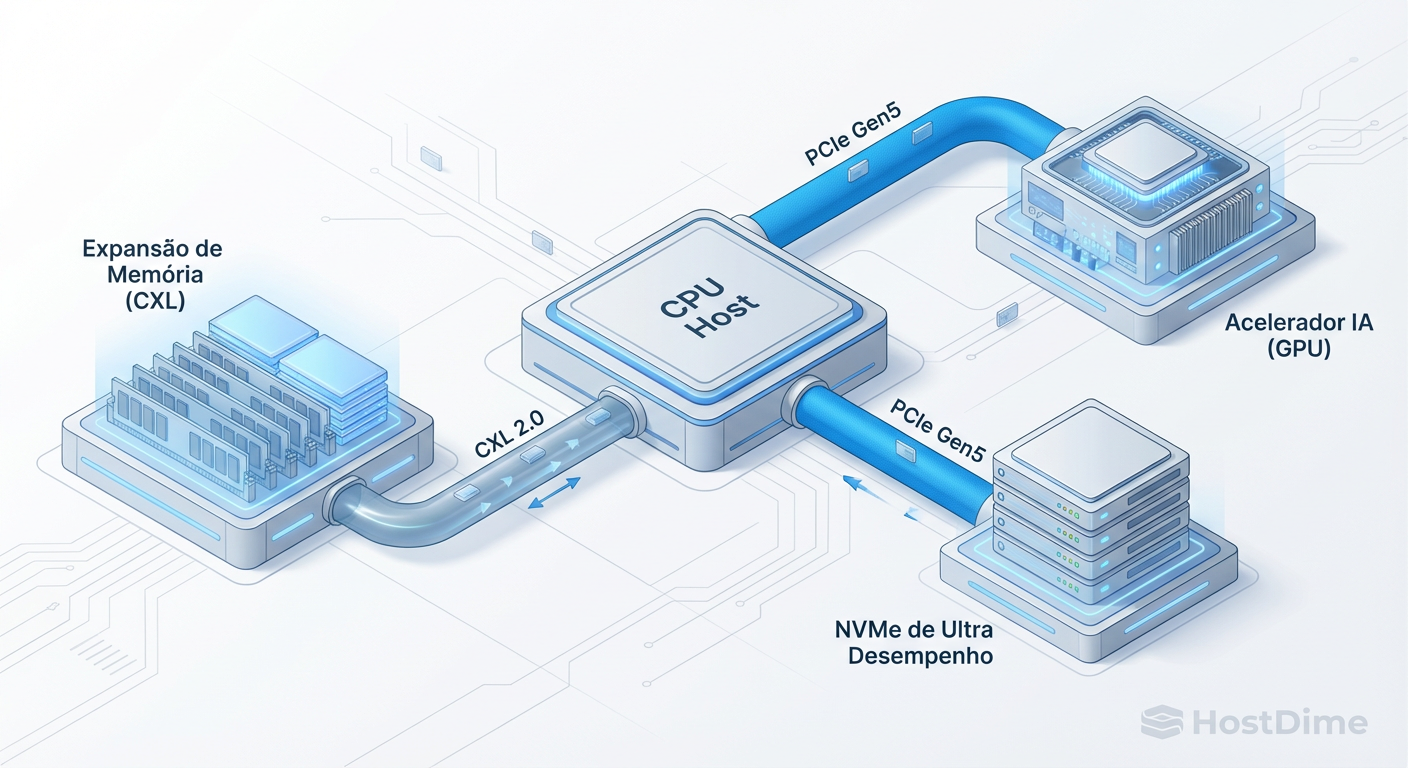

Falar de PCIe Gen5 sem mencionar o CXL (Compute Express Link) é ignorar metade da proposta de valor. O CXL é um protocolo aberto construído sobre a camada física do PCIe Gen5 que permite coerência de cache entre a CPU e dispositivos aceleradores ou memória.

Existem três protocolos principais que alteram nossas opções de design:

CXL.io: Similar ao PCIe tradicional (descoberta, configuração).

CXL.cache: Permite que aceleradores acessem a memória da CPU de forma coerente.

CXL.mem: Permite que a CPU acesse a memória do acelerador (ou memória expandida) como se fosse sua própria RAM.

Isso habilita uma nova topologia onde podemos adicionar memória RAM via slots PCIe, desacoplando a capacidade de memória da quantidade de canais da CPU.

Figura: Fig. 2: Topologia moderna habilitada pelo Gen5, introduzindo o conceito de CXL para expansão de memória e coerência de cache.

Figura: Fig. 2: Topologia moderna habilitada pelo Gen5, introduzindo o conceito de CXL para expansão de memória e coerência de cache.

Trade-offs de Implementação: Custo Térmico, Preço por Lane e Compatibilidade

Como arquitetos, devemos ser céticos. A performance extra do Gen5 vem com custos ocultos que impactam diretamente o OpEx (Operational Expenditure) e a complexidade de manufatura.

1. Integridade de Sinal e Custo da PCB

A frequência de 32 GHz do Gen5 sofre atenuação severa em materiais de PCB padrão (FR4). Para implementar Gen5, os fabricantes de servidores devem usar materiais de perda ultra-baixa (Ultra Low Loss), que são significativamente mais caros. Além disso, o alcance do sinal é curto. Se o slot PCIe estiver longe da CPU (na borda traseira de um chassi profundo), o sinal morrerá antes de chegar. Isso obriga o uso de Retimers (chips que regeneram o sinal), adicionando:

Custo de componente ($15-$25 por chip).

Latência (na casa dos nanossegundos, geralmente negligenciável, mas existente).

Consumo de energia adicional.

2. Desafios Térmicos

O aumento da densidade de potência não ocorre apenas na CPU. Controladores NVMe Gen5 e retimers esquentam. Em um data center denso, isso pode exigir uma mudança de refrigeração a ar para refrigeração líquida (DLC - Direct Liquid Cooling) ou, no mínimo, dissipadores de calor mais agressivos que ocupam mais volume, reduzindo potencialmente o fluxo de ar para outros componentes.

3. O Trade-off da Compatibilidade

A boa notícia é a retrocompatibilidade. Você pode colocar uma placa Gen4 em um slot Gen5. No entanto, o inverso — colocar uma placa Gen5 em um sistema Gen4 — desperdiça 50% do investimento feito naquele componente, pois ele negociará a velocidade para baixo.

A pergunta crítica de TCO: O prêmio de preço de um servidor habilitado para Gen5 (placa-mãe mais cara, retimers, fontes maiores) é compensado pela consolidação de workloads?

Se você pode substituir 2 servidores Gen4 por 1 servidor Gen5 devido à remoção de gargalos de I/O, o TCO é positivo.

Se o servidor continua limitado pela CPU, você apenas aumentou o CapEx sem retorno.

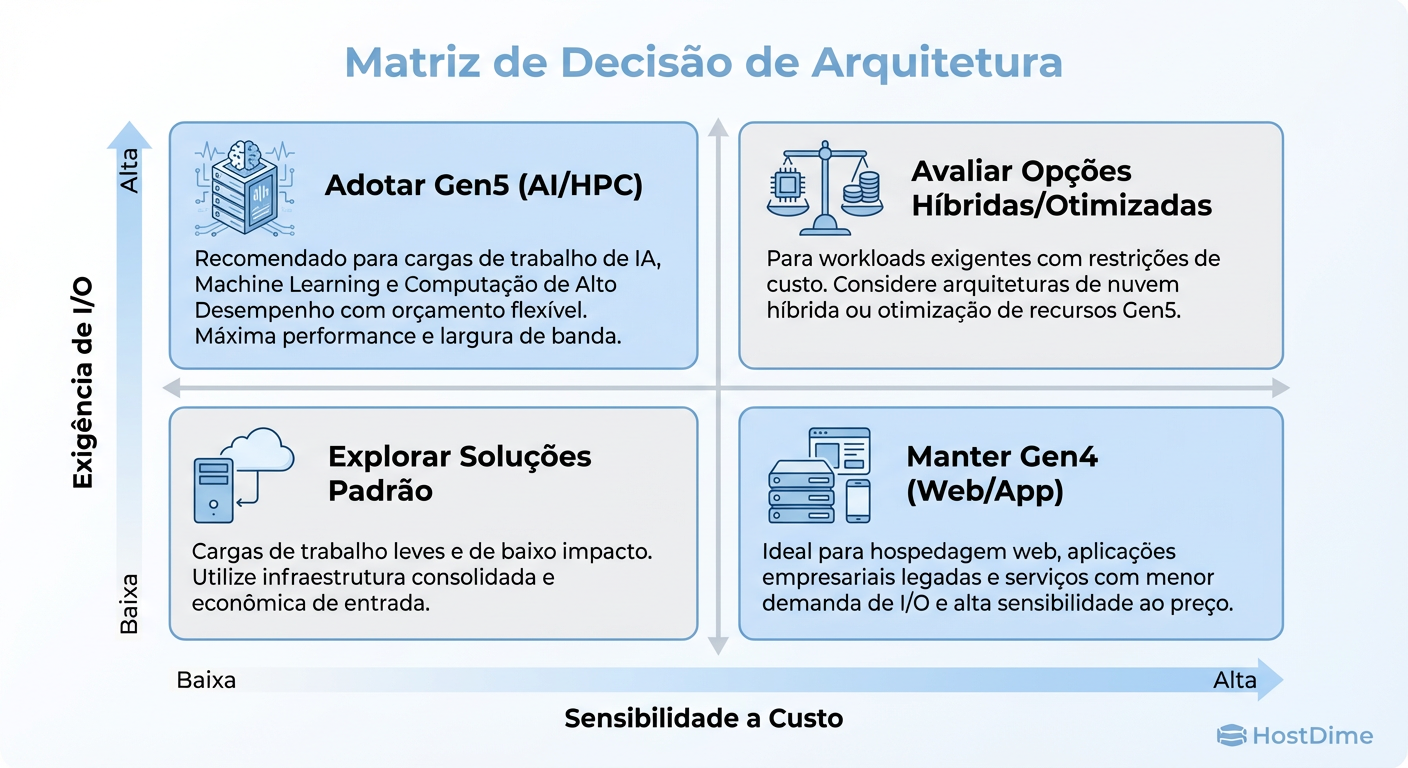

Decisão Recomendada: Matriz de Escolha baseada em Workload

Não existe "bala de prata". A decisão de migrar para PCIe Gen5 deve ser baseada estritamente no perfil do workload e na análise de gargalos atuais.

Abaixo, apresento uma matriz de decisão estratégica para guiar a adoção.

Figura: Fig. 3: Matriz de Decisão Estratégica para adoção de PCIe Gen5 baseada em TCO e requisitos de I/O.

Figura: Fig. 3: Matriz de Decisão Estratégica para adoção de PCIe Gen5 baseada em TCO e requisitos de I/O.

Análise dos Cenários

Cenário A: High-Frequency Trading (HFT) e AI Training

Recomendação: Adoção Imediata (Gen5). Justificativa: Em HFT, cada nanossegundo conta. A latência reduzida e a largura de banda para ingestão de dados de mercado são vantagens competitivas diretas. Em AI, a fome das GPUs H100/A100 por dados torna o barramento o principal limitador. O custo do hardware é irrelevante comparado ao custo de cientistas de dados ociosos ou tempo de treinamento prolongado.

Cenário B: Bancos de Dados In-Memory e Analytics

Recomendação: Adoção Estratégica (Gen5 com CXL). Justificativa: Aqui, o valor não está apenas na velocidade, mas na capacidade de memória. Utilizar CXL para expandir a RAM via barramento PCIe pode ser mais barato do que preencher todos os canais de memória com DIMMs de alta densidade (e custo proibitivo).

Cenário C: Web Servers, App Servers e Microservices

Recomendação: Manter Gen4 (ou até Gen3). Justificativa: A maioria das aplicações web são limitadas por latência de rede externa, banco de dados ou processamento de lógica de negócios (CPU). O tráfego de I/O raramente satura um link Gen4 x4, quem dirá x16. Migrar para Gen5 aqui é "gold plating" — gastar dinheiro em sofisticação desnecessária.

Cenário D: Storage Arrays (SDS - Software Defined Storage)

Recomendação: Avaliar Densidade. Justificativa: Se o objetivo é máxima densidade (ex: 24 NVMe drives em 2U), o Gen5 é necessário para não criar um gargalo no uplink para a rede. Se o storage é HDD ou SSD SATA/SAS, o Gen5 é desnecessário.

Visão de Longo Prazo: A preparação para PCIe Gen6 e a Era da Memória Desagregada

Como arquitetos, devemos olhar para o horizonte de 3 a 5 anos. O PCIe Gen5 é, em muitos aspectos, uma tecnologia de transição e fundação para o que virá com o PCIe Gen6 e o amadurecimento do CXL.

O Gen6 mudará a codificação para PAM4 (Pulse Amplitude Modulation 4-level), dobrando novamente a velocidade para 64 GT/s. Isso trará a correção de erro (FEC) mandatória, o que adicionará latência. Portanto, para aplicações sensíveis à latência pura, o Gen5 pode, ironicamente, ser mais "snappy" em certos cenários de baixa carga do que as primeiras implementações de Gen6 devido ao overhead do FEC.

A Era da Infraestrutura Composable

A visão de longo prazo é a desagregação total. Hoje, compramos servidores com quantidades fixas de CPU, RAM e Storage. Com a evolução do PCIe Gen5/6 e CXL, caminhamos para o Rack-Scale Architecture:

Um chassi apenas de computação (CPUs).

Um chassi apenas de memória (Memory Pools).

Um chassi de aceleradores (GPUs/DPUs).

Tudo conectado via barramento PCIe/CXL estendido ou cabeado. Isso permitirá que o orquestrador (Kubernetes, por exemplo) componha um "servidor lógico" no momento do deploy, alocando exatos 16 cores e 512GB de RAM de pools distintos.

Investir em Gen5 hoje e entender CXL é o primeiro passo para preparar sua organização para essa mudança de paradigma, saindo de servidores monolíticos para uma infraestrutura líquida e dinâmica.

Veredito Técnico

A decisão de adotar PCIe Gen5 não deve ser impulsionada pelo medo de ficar obsoleto (FOMO), mas por uma análise fria de gargalos. Para a maioria das cargas de trabalho corporativas padrão, o Gen4 permanece a escolha de melhor TCO. No entanto, para a vanguarda da computação (AI, HPC, Real-Time Analytics), o Gen5 não é um luxo, é oxigênio.

Arquitetar é fazer escolhas difíceis sobre onde gastar o orçamento de complexidade. Escolha sabiamente.

Referências

PCI-SIG. "PCI Express Base Specification Revision 5.0". PCI Special Interest Group, 2019.

Compute Express Link Consortium. "CXL 2.0 Specification: Evaluation Guide". CXL Consortium, 2020.

Open Compute Project (OCP). "Server Design Specifications for High-Performance Computing".

Hennessy, J. L., & Patterson, D. A. "Computer Architecture: A Quantitative Approach". (Conceitos de Amdahl's Law e I/O Bottlenecks).

Vogels, Werner. "The Frugal Architect". All Things Distributed, 2023. (Conceitos de TCO e Custo como Requisito Não-Funcional).

Roberto Uchoa

Sysadmin Veterano (Anti-Hype)

"Sobrevivente da bolha pontocom e do hype do Kubernetes. Troco qualquer arquitetura de microsserviços 'inovadora' por um script bash que funciona sem falhas há 15 anos. Uptime não é opcional."