PCIe Gen5 no Data Center: Análise de TCO, Performance e Adoção Estratégica

Descubra se o PCIe Gen5 vale o investimento para sua infraestrutura. Análise de arquiteto sobre gargalos de I/O, CXL, custos térmicos e casos de uso reais.

Na arquitetura de sistemas distribuídos e infraestrutura de alta performance, a resposta padrão para qualquer decisão de upgrade é sempre a mesma: depende. A migração para o PCI Express 5.0 (PCIe Gen5) não foge a essa regra. Embora os números de marketing destaquem o dobro de largura de banda em relação à geração anterior, a realidade no chão do Data Center envolve uma equação complexa de Custo Total de Propriedade (TCO), maturidade do ecossistema e requisitos reais das cargas de trabalho (workloads).

Como arquitetos, não devemos perseguir especificações técnicas por vaidade. Devemos resolver problemas de negócio. Este artigo analisa a viabilidade do PCIe Gen5 sob a ótica da engenharia de soluções enterprise, ponderando se o salto de performance justifica o prêmio de custo e complexidade térmica.

O Problema de Negócio: O Gargalo de I/O na Era da IA Generativa

O cenário atual de computação mudou drasticamente. Até recentemente, a maioria das aplicações corporativas era limitada pela CPU (Compute-bound). Hoje, com a ascensão meteórica da IA Generativa e dos Large Language Models (LLMs), o gargalo deslocou-se agressivamente para a entrada e saída de dados (I/O-bound).

GPUs modernas, como as baseadas na arquitetura NVIDIA Hopper ou AMD CDNA 3, possuem um apetite voraz por dados. Manter esses aceleradores — que custam dezenas de milhares de dólares cada — ociosos esperando por dados é um erro financeiro imperdoável.

O problema de negócio que o PCIe Gen5 visa resolver não é apenas "transferir arquivos mais rápido", mas sim maximizar a utilização de ativos caros. Se o barramento de comunicação não consegue alimentar a VRAM da GPU na velocidade necessária, ou se o armazenamento NVMe satura o link antes da CPU, estamos desperdiçando capital.

No entanto, a largura de banda não é o único fator. A latência e a eficiência energética por bit transferido tornaram-se métricas críticas em um mundo onde o power budget do rack é finito.

Opções Arquiteturais: Permanecer no Gen4 vs. Migração para Gen5

A decisão arquitetural primária reside entre manter a infraestrutura baseada em PCIe Gen4 (madura, commoditizada) ou migrar para o bleeding edge do Gen5.

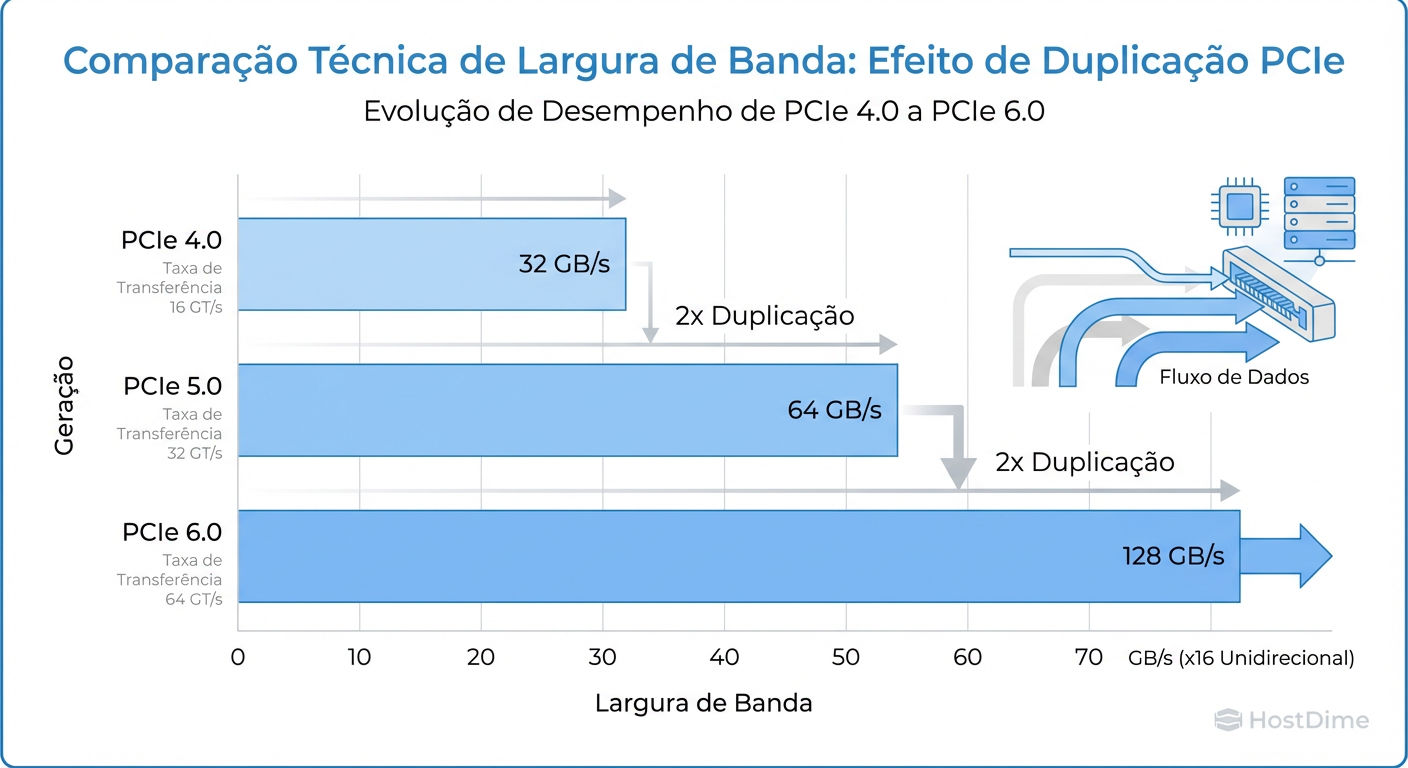

Para contextualizar, o PCIe Gen4 oferece 16 GT/s (Gigatransfers por segundo) por lane. O PCIe Gen5 dobra isso para 32 GT/s. Em um slot x16 típico de uma placa aceleradora, isso significa saltar de ~64 GB/s para ~128 GB/s de largura de banda bidirecional teórica.

Figura: Fig 1. Evolução da Taxa de Transferência por Lane: O salto de performance do Gen4 para o Gen5 e a projeção para o Gen6.

Figura: Fig 1. Evolução da Taxa de Transferência por Lane: O salto de performance do Gen4 para o Gen5 e a projeção para o Gen6.

Opção A: Permanecer no Gen4

Esta é a escolha conservadora e, muitas vezes, a mais sensata para workloads tradicionais (bancos de dados relacionais padrão, servidores web, virtualização geral). A cadeia de suprimentos é estável, os custos de placas-mãe são conhecidos e os desafios térmicos são gerenciáveis.

Opção B: Migração para Gen5

Esta opção é mandatória para clusters de HPC (High Performance Computing) e treinamento de IA. A arquitetura Gen5 não apenas aumenta a velocidade, mas habilita novas topologias de interconexão e protocolos como o CXL (Compute Express Link), que discutiremos adiante. Contudo, essa opção traz uma complexidade de engenharia física que não pode ser ignorada.

Trade-offs Técnicos: Integridade de Sinal, Desafios Térmicos e Custo por Lane

Aqui reside a análise crítica de TCO. O dobro de frequência do Gen5 introduz desafios físicos severos. A lei da física é implacável: quanto maior a frequência, maior a atenuação do sinal (insertion loss) ao percorrer o cobre da placa de circuito impresso (PCB).

1. Integridade de Sinal e Custo do PCB

No PCIe Gen4, podíamos utilizar materiais de PCB de "perda média" e traços relativamente longos. No Gen5, a tolerância para perda de sinal é muito menor (o orçamento de perda total é de -36dB). Isso obriga os fabricantes de servidores a utilizar materiais de PCB de perda ultra-baixa (como Megtron 6 ou 7), que são significativamente mais caros. Além disso, o design da placa exige um roteamento mais preciso para evitar crosstalk.

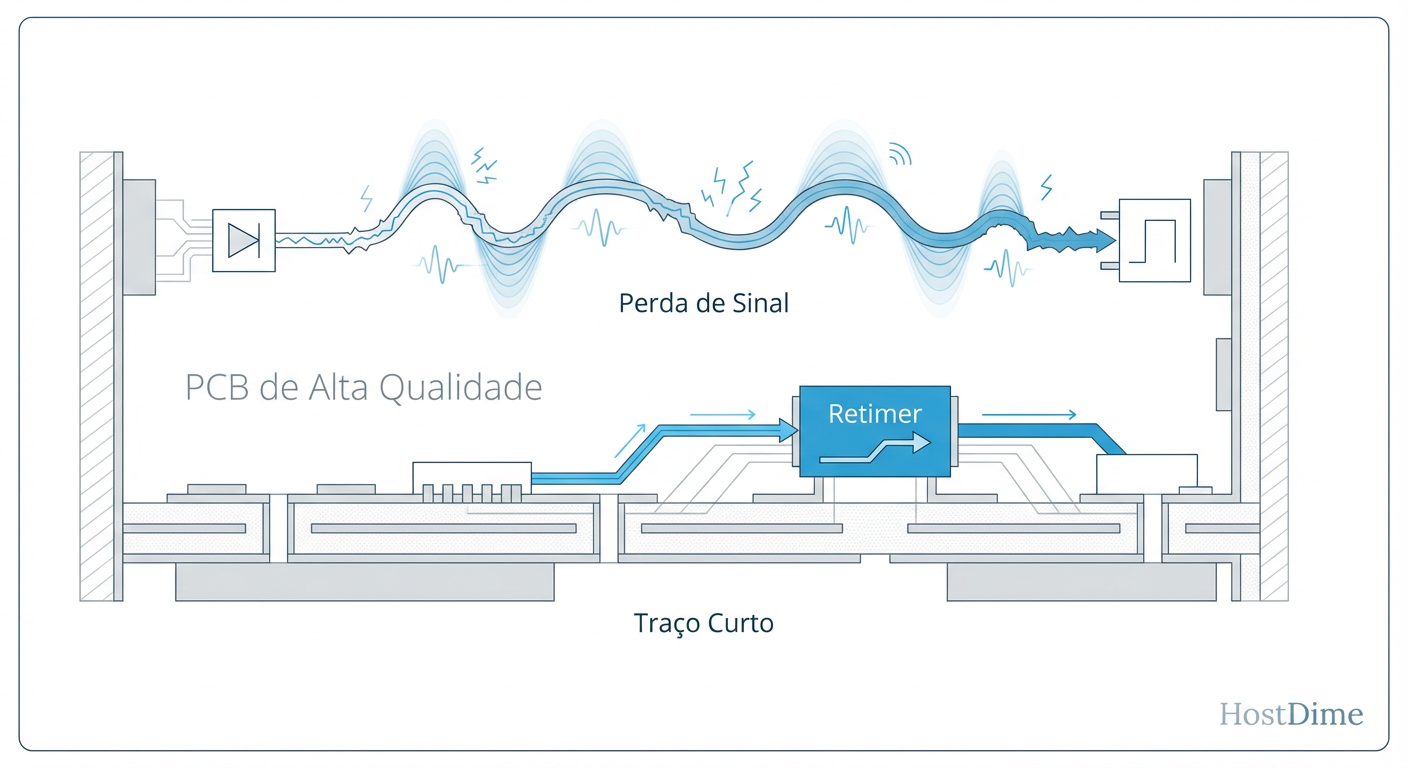

2. A Necessidade de Retimers

Para mitigar a degradação do sinal em distâncias maiores que alguns poucos polegadas, a arquitetura Gen5 exige o uso extensivo de Retimers. Diferente dos Redrivers (que apenas amplificam o sinal analógico), os Retimers decodificam o sinal, recuperam os dados e o retransmitem limpo.

Impacto no Custo: Retimers são chips caros e complexos.

Impacto na Latência: Adicionam uma latência residual (na casa dos nanossegundos), embora compensada pela velocidade do link.

Impacto Energético: Consumam energia e geram calor adicional na placa-mãe.

Figura: Fig 3. O custo oculto: A física da integridade de sinal no Gen5 exige traços mais curtos e uso intensivo de retimers, elevando o custo da placa-mãe.

Figura: Fig 3. O custo oculto: A física da integridade de sinal no Gen5 exige traços mais curtos e uso intensivo de retimers, elevando o custo da placa-mãe.

3. Densidade Térmica

Com SSDs NVMe Gen5 atingindo velocidades de leitura sequencial acima de 14 GB/s, os controladores desses discos aquecem rapidamente. Em um servidor 1U ou 2U denso, o fluxo de ar torna-se um desafio de engenharia. Dissipadores de calor maiores nos SSDs e fluxo de ar turbulento podem exigir ventoinhas operando em RPMs mais altas, aumentando o consumo de energia do chassi (OPEX).

Onde é Realidade: SSDs NVMe Enterprise e Aceleradores de IA

A adoção do PCIe Gen5 não é uniforme. Ela ocorre em bolsões onde o ROI é justificável.

Armazenamento de Alta Performance (NVMe)

Para aplicações de Big Data Analytics e Cache Tiering, o Gen5 é uma realidade. SSDs Enterprise Gen5 (EDSFF E1.S ou E3) estão sendo implantados para alimentar data lakes que exigem throughput massivo. A capacidade de ler dados a 14-16 GB/s por drive permite que menos drives saturem a capacidade de processamento da CPU, potencialmente reduzindo o número de servidores necessários para atingir um determinado SLA de IOPS.

Aceleradores de IA e GPUs

Este é o principal driver de adoção. As interconexões entre CPU e GPU (quando não utilizam tecnologias proprietárias como NVLink para tudo) dependem do PCIe. Para alimentar uma GPU H100, o PCIe Gen5 é o requisito mínimo para evitar que o barramento seja o gargalo durante o carregamento de weights de modelos massivos.

Onde ainda é Nicho: CXL (Compute Express Link) e Networking Generalista

Embora tecnicamente viável, nem toda área do Data Center precisa do Gen5 imediatamente.

Networking Generalista

Placas de rede (NICs) de 100GbE funcionam perfeitamente em PCIe Gen4 x16 (ou até x8). A necessidade de Gen5 surge apenas quando migramos para 400GbE ou 800GbE. A menos que seu Data Center esteja fazendo o upgrade do backbone para 400G+, o Gen5 no networking de borda pode ser um overkill.

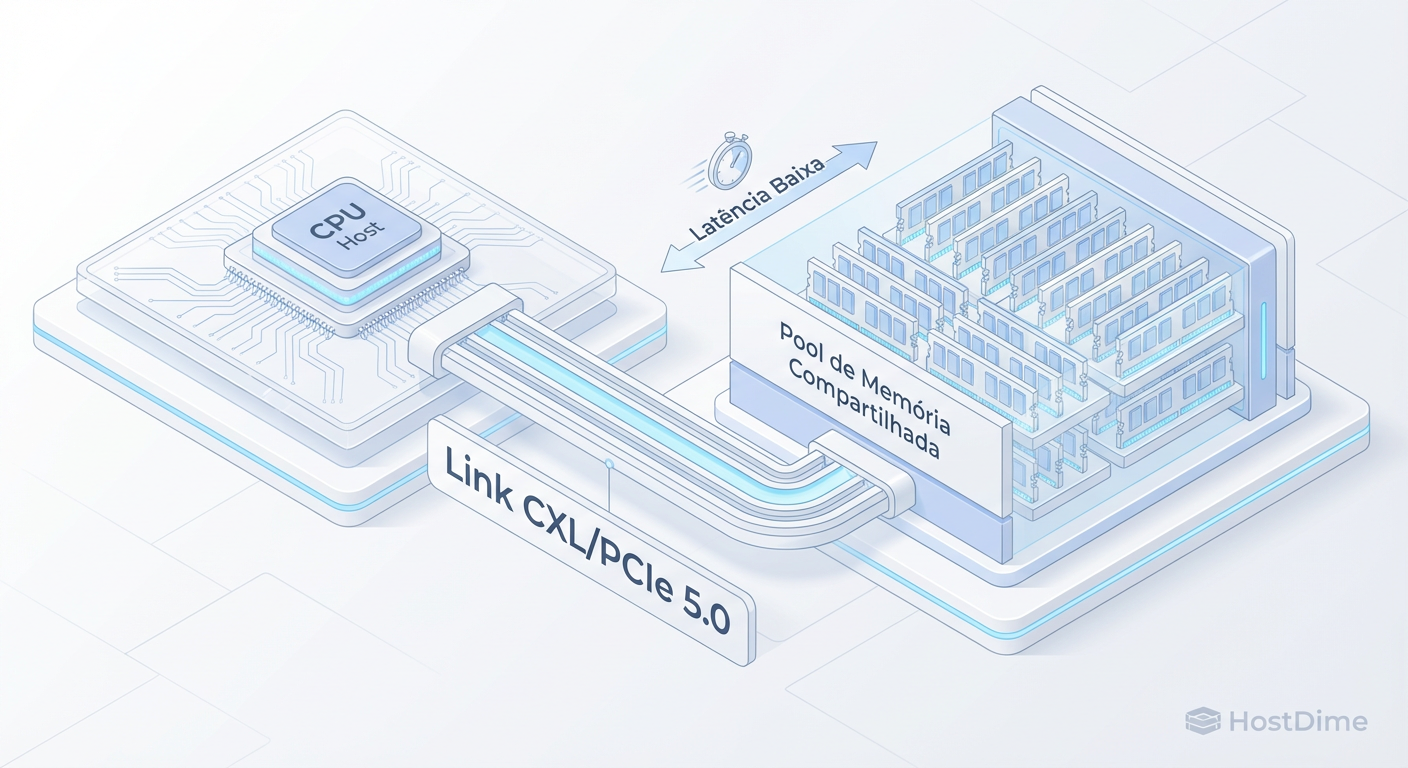

A Promessa do CXL (Compute Express Link)

O CXL é, talvez, a revolução mais importante habilitada pelo ecossistema elétrico do PCIe Gen5. Ele permite a coerência de cache entre a CPU e dispositivos acoplados. Isso abre portas para a Desagregação de Memória. Imagine um pool de memória RAM que não está preso a um servidor específico, mas pode ser alocado dinamicamente para onde a demanda existe.

Figura: Fig 2. O futuro da arquitetura 'Composable': Como o PCIe Gen5 habilita o protocolo CXL para desagregar a memória RAM.

Figura: Fig 2. O futuro da arquitetura 'Composable': Como o PCIe Gen5 habilita o protocolo CXL para desagregar a memória RAM.

No entanto, embora o hardware (CPUs Sapphire Rapids, Genoa) suporte CXL 1.1/2.0, o suporte de software e a disponibilidade de módulos de memória CXL ainda são nicho. É uma aposta estratégica de longo prazo, não uma solução de prateleira para a maioria das empresas hoje.

Decisão Recomendada: Matriz de Decisão baseada em Workloads

Como arquitetos, devemos guiar a decisão baseada no valor de negócio. Abaixo, apresento uma matriz de decisão simplificada para orientar a adoção.

| Carga de Trabalho (Workload) | Recomendação Arquitetural | Justificativa (Trade-off) |

|---|---|---|

| Treinamento de LLMs / IA Generativa | Adotar PCIe Gen5 | O custo da ociosidade da GPU supera o custo extra da infraestrutura. A largura de banda é crítica. |

| Bancos de Dados In-Memory (SAP HANA, Redis) | Avaliar Gen5 / CXL | Se a capacidade de RAM por soquete for um limitante, Gen5 com CXL é transformador. Caso contrário, Gen4 basta. |

| Virtualização Geral / VDI | Manter PCIe Gen4 | A densidade de VM raramente é limitada pelo barramento PCIe. O custo extra do Gen5 prejudica o TCO por VM. |

| Storage Arrays (All-Flash) | Adotar PCIe Gen5 | Permite dobrar a densidade de performance ou reduzir pela metade o número de lanes necessárias por drive. |

| Web Servers / App Servers | Manter PCIe Gen4 | O gargalo geralmente é a latência de rede externa ou lógica de aplicação, não o barramento local. |

Veredito: Adote o Gen5 onde a densidade de I/O for o fator limitante de escalabilidade vertical. Para o restante, a maturidade e o custo do Gen4 ainda oferecem o melhor TCO.

Visão de Longo Prazo: A Preparação para PCIe Gen6 e Infraestrutura Composable

Olhando para o horizonte, o PCIe Gen5 é, de certa forma, uma tecnologia de transição. O PCIe Gen6 já está especificado e trará uma mudança fundamental: a alteração da codificação de NRZ (Non-Return-to-Zero) para PAM4 (Pulse Amplitude Modulation 4-level).

Isso significa que o Gen6 dobrará novamente a velocidade (64 GT/s) utilizando a mesma frequência base do Gen5, mas transmitindo dois bits por ciclo de clock.

Por que isso importa hoje? Ao investir em infraestrutura Gen5 (chassis, backplanes, risers), é vital verificar a compatibilidade futura ou a vida útil desses ativos. A complexidade de integridade de sinal do Gen5 preparou o terreno para o Gen6. As lições aprendidas com retimers e materiais de PCB de baixa perda hoje serão a base para a infraestrutura Composable de amanhã.

A visão de longo prazo é um Data Center onde CPU, GPU, Memória e Storage são recursos desagregados, conectados por um fabric de alta velocidade (CXL sobre PCIe), compondo servidores lógicos on-the-fly. O PCIe Gen5 é o primeiro passo concreto nessa direção.

Para o arquiteto enterprise, a recomendação é: não espere pelo Gen6 se o seu negócio está sofrendo hoje, mas desenhe sua infraestrutura Gen5 sabendo que ela é a fundação para um futuro modular e desagregado.

Referências

PCI-SIG. "PCI Express Base Specification Revision 5.0". PCI Special Interest Group, 2019.

Compute Express Link Consortium. "CXL 2.0 Specification". CXL Consortium, 2020.

Vogels, Werner. "Distributing the Future". All Things Distributed, Amazon.

Hennessy, J. L., & Patterson, D. A. "Computer Architecture: A Quantitative Approach". Morgan Kaufmann.

Micron Technology. "The Impact of PCIe Gen5 on Data Center SSDs". Technical Whitepaper, 2023.

Rafael Barros

Arquiteto de Cloud Storage

"Desenho arquiteturas de object storage escaláveis e guiadas por API. Meu foco é performance máxima sem deixar o orçamento sangrar com taxas de egress ocultas."