Memórias Probabilísticas e Storage Class Memory: PCM, ReRAM e a Realidade dos Estados Instáveis

Entenda a física e os trade-offs do PCM e ReRAM. Uma análise técnica sobre Storage Class Memory, drift de resistência e por que o futuro do armazenamento lida com probabilidades, não apenas bits estáticos.

Você olha para o painel de monitoramento. A latência de I/O disparou, mas não há erros de disco no dmesg. O throughput está baixo, mas a CPU está ociosa, esperando. O culpado não é o software, e talvez nem seja o disco rígido mecânico que você já aposentou anos atrás. O problema reside em um "limbo" físico que a indústria de hardware tenta esconder de você há uma década.

Como investigador forense de sistemas, aprendi a desconfiar do termo "estado sólido". Quando descemos ao nível nanométrico, nada é verdadeiramente sólido ou estático. Estamos lidando com a física quântica e termodinâmica tentando se comportar como zeros e uns confiáveis.

A indústria nos vendeu a ideia de que o Storage Class Memory (SCM) — tecnologias como PCM (Phase Change Memory) e ReRAM (Resistive RAM) — seria o "elo perdido" que unificaria a velocidade da DRAM com a persistência do SSD. A realidade, porém, é muito mais caótica. Ao contrário dos capacitores da DRAM ou das armadilhas de carga da NAND Flash, essas novas memórias dependem de alterar a estrutura física da matéria. E a matéria, por natureza, odeia ficar parada.

Storage Class Memory (SCM) é uma arquitetura de memória não-volátil que preenche o abismo de latência entre a DRAM (nanossegundos) e o SSD NAND (microssegundos). Diferente da Flash, que armazena carga elétrica, o SCM (como PCM e ReRAM) altera a resistência física do material, permitindo endereçamento por byte e durabilidade superior, mas introduzindo desafios de instabilidade de estado conhecidos como "Resistance Drift".

O Abismo de Latência e a Necessidade do SCM

Para entender o crime, precisamos entender o motivo. Por décadas, operamos com um gargalo brutal na hierarquia de memória.

DRAM: É rápida (latência de ~10-100ns), mas volátil e cara. Se a energia cair, os dados somem.

NAND Flash (SSD): É persistente e densa, mas lenta em comparação à CPU (latência de ~10-100µs).

O processador passa milhares de ciclos "dormindo" enquanto espera o SSD buscar um dado. O SCM surgiu para habitar esse meio-termo, oferecendo latências próximas à DRAM com a persistência da Flash. Mas para conseguir isso, a engenharia teve que abandonar o elétron e começar a mexer com a estrutura atômica.

A Física da Resistência no PCM e ReRAM: Baldes vs. Canos

Aqui é onde a maioria dos administradores de storage se perde. Estamos acostumados com o modelo mental da Flash NAND ou da DRAM, que funcionam como baldes. Você enche o balde de elétrons (carga) para representar um "0" e esvazia para um "1". O problema do balde é que ele vaza (na DRAM) ou se desgasta ao ser enchido e esvaziado violentamente (na Flash).

As memórias resistivas (PCM, ReRAM) funcionam de forma diferente. Elas não armazenam "coisas". Elas alteram a capacidade do meio de conduzir eletricidade. Pense nelas como um cano de água que pode mudar de diâmetro.

Figura: Modelo Mental: Carga vs. Resistência. Enquanto a Flash vaza elétrons (balde furado), o PCM e ReRAM sofrem alterações na própria estrutura do material (o cano muda de largura), criando o fenômeno do Resistance Drift.

Figura: Modelo Mental: Carga vs. Resistência. Enquanto a Flash vaza elétrons (balde furado), o PCM e ReRAM sofrem alterações na própria estrutura do material (o cano muda de largura), criando o fenômeno do Resistance Drift.

PCM (Phase Change Memory): O Legado do 3D XPoint

A tecnologia mais famosa dessa classe foi o 3D XPoint (comercializado pela Intel como Optane). O PCM usa um vidro calcogeneto.

Para gravar: Você aplica calor. Um pulso curto e intenso derrete o material e o resfria rapidamente, deixando-o em estado amorfo (alta resistência, o cano fica estreito). Um pulso longo e suave cristaliza o material (baixa resistência, o cano fica largo).

A Vantagem: Write-in-Place. Diferente da Flash, você não precisa apagar um bloco inteiro antes de gravar. Você apenas muda o estado da célula. Isso reduz drasticamente a latência de gravação e aumenta a vida útil.

ReRAM (Resistive RAM): A Formação de Filamentos

A ReRAM (ou RRAM) opera criando e destruindo filamentos condutores dentro de um material dielétrico. Imagine um raio microscópico que conecta dois eletrodos.

Set (Gravar): Aplica-se voltagem para formar o filamento (baixa resistência).

Reset (Apagar): Aplica-se voltagem inversa para romper o filamento (alta resistência).

O problema forense aqui é a palavra "estocástico". A formação desses filamentos não é perfeitamente geométrica. Ela é probabilística. O filamento cresce como uma raiz de árvore, nunca exatamente igual duas vezes.

A Ilusão do Bit Estático e o Fenômeno do Resistance Drift

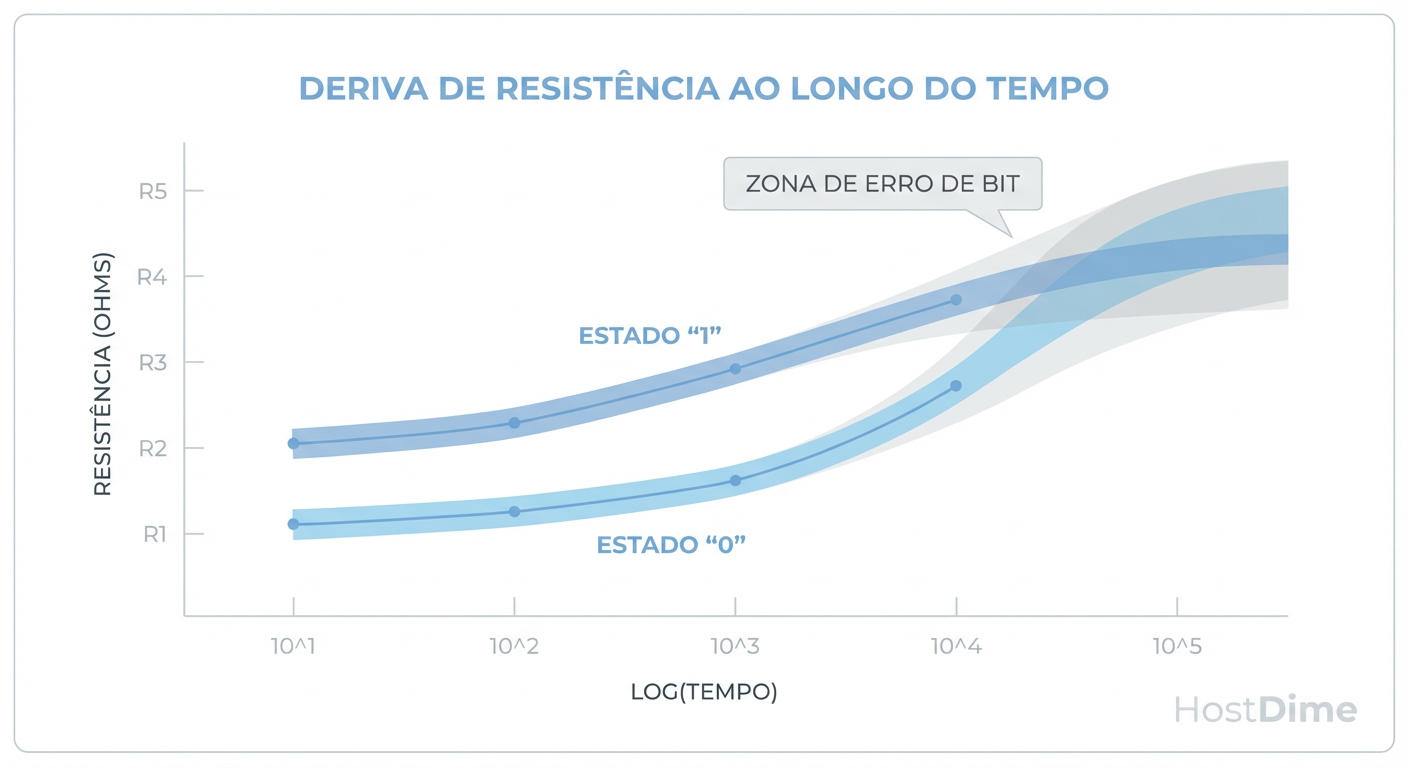

Se você acredita que, uma vez gravado, o dado no SCM permanece imutável até a próxima gravação, você está enganado. Bem-vindo ao pesadelo do Resistance Drift (Deriva de Resistência).

Em materiais de mudança de fase (PCM), o estado amorfo (alta resistência) é termodinamicamente instável. Com o tempo, os átomos tentam se "relaxar" para uma configuração de menor energia. Isso faz com que a resistência elétrica da célula aumente lentamente ao longo do tempo, mesmo sem nenhuma operação de escrita.

Figura: O Inimigo Silencioso: Resistance Drift. Com o tempo, a resistência física do material tende a aumentar, fazendo com que os estados lógicos '0' e '1' se confundam, exigindo controladores complexos para rastrear essas mudanças.

Figura: O Inimigo Silencioso: Resistance Drift. Com o tempo, a resistência física do material tende a aumentar, fazendo com que os estados lógicos '0' e '1' se confundam, exigindo controladores complexos para rastrear essas mudanças.

Por que isso é um risco para a integridade dos dados?

Imagine que definimos:

Resistência 100Ω a 500Ω = Bit "1"

Resistência 1000Ω a 5000Ω = Bit "0"

Você grava um "1" (200Ω). Passam-se dias ou meses. O material relaxa. A resistência sobe para 600Ω, depois 800Ω. De repente, quando o controlador lê aquela célula, ele entra numa "zona cinzenta" ou, pior, interpreta erroneamente como um "0".

Isso exige controladores de memória extremamente agressivos que realizam "scrubbing" (limpeza) constante, lendo e reescrevendo dados apenas para garantir que a resistência volte ao patamar correto. Se você desligar um servidor com SCM por um longo período em alta temperatura, o risco de corrupção de dados por drift é real e mensurável.

Comparativo Técnico: DRAM vs NAND vs SCM

Para decidir onde aplicar essas tecnologias, precisamos olhar para os números frios. O SCM não substitui a DRAM nem a NAND; ele cria uma nova camada.

| Característica | DRAM (DDR5) | SCM (Optane/PCM/ReRAM) | NAND Flash (TLC/QLC) |

|---|---|---|---|

| Latência de Leitura | ~15-20 ns | ~100-300 ns | ~80-100 µs |

| Persistência | Volátil (perde dados sem energia) | Não-Volátil | Não-Volátil |

| Endereçamento | Byte-addressable (acesso direto) | Byte-addressable | Block-addressable (páginas/blocos) |

| Resistência (Writes) | >10^15 (praticamente infinita) | ~10^8 a 10^9 | ~10^3 a 10^4 (ciclos P/E) |

| Mecanismo de Falha | Vazamento de capacitor | Resistance Drift / Falha de cristalização | Degradação do óxido (tunneling) |

| Custo por GB | Alto ($$$$) | Médio ($$$) | Baixo ($) |

Neuromorphic Computing: Quando o Bug vira Feature

Aqui entra uma reviravolta interessante. O comportamento probabilístico e "analógico" da ReRAM e do PCM é um pesadelo para armazenamento de arquivos (onde exigimos precisão binária absoluta), mas é o Santo Graal para a Computação Neuromórfica.

Redes neurais não precisam de zeros e uns perfeitos; elas precisam de "pesos" (weights). A condutância variável de um memristor (ReRAM) funciona de forma assustadoramente similar a uma sinapse biológica.

No Storage: O Resistance Drift é corrupção de dados.

Na IA: A variação de condutância permite realizar multiplicação de matrizes diretamente na memória (Compute-in-Memory), economizando a energia de mover dados para a CPU.

Se você está investigando um sistema focado em inferência de IA na borda (Edge AI) que usa ReRAM, a "instabilidade" pode ser intencional. Não a trate como falha de hardware sem verificar a aplicação.

O Veredito Prático: O Futuro com CXL

A morte comercial do Intel Optane para consumidores (discos SSD) não matou a tecnologia PCM; apenas a reposicionou. O futuro dessas memórias instáveis, porém rápidas, não está no slot M.2 ou U.2, mas no barramento de memória via CXL (Compute Express Link).

O CXL permite conectar pools de memória SCM diretamente ao processador com coerência de cache. Isso significa que podemos ter servidores com Terabytes de memória "lenta" (SCM) mas persistente, acessível como se fosse RAM.

Checklist de Sobrevivência para Arquitetos de Storage

Não confie na retenção térmica: Se você usa SCM para dados críticos cold storage (desligado), verifique as especificações de retenção de dados versus temperatura. O calor acelera o Resistance Drift.

Monitore o Media Wearout: Diferente da Flash, que falha ao não conseguir apagar, o PCM falha ao não conseguir mudar de estado (stuck-set ou stuck-reset). As métricas SMART são diferentes.

Use CXL para expansão, não substituição: Use SCM via CXL para bancos de dados in-memory (Redis, SAP HANA) onde a recuperação rápida pós-reboot é vital, mas mantenha backups em NAND ou fita. A probabilidade nunca é zero.

A era do armazenamento probabilístico chegou. O bit não é mais um tijolo; é uma probabilidade estatística de resistência elétrica. Ajuste seus modelos mentais e suas ferramentas de monitoramento, ou o drift levará seus dados embora silenciosamente.

Referências & Leitura Complementar

JEDEC DDR5 & NVDIMM Standards: Especificações técnicas sobre a integração de memórias persistentes no barramento de memória.

Intel Optane DC Persistent Memory Product Specifications: Documentação técnica detalhando os modos "Memory Mode" e "App Direct" e as características de latência do 3D XPoint.

"The Missing Memristor has Not been Found" (Nature, Strukov et al.): O paper fundamental que ligou a teoria do memristor à realidade física da ReRAM.

SNIA (Storage Networking Industry Association): Whitepapers sobre programação de Memória Persistente (PMDK).

Bruno Azevedo

Especialista em Performance de I/O

Obscecado por latência zero. Analisa traces de kernel e otimiza drivers de storage para bancos de dados de alta frequência.