CXL 3.1: O fim do gargalo de memória em bancos de dados de alta performance

Descubra como o CXL 3.1 e a memória desagregada eliminam o 'Memory Wall' em bancos de dados, reduzindo o TCO e permitindo pools de RAM de múltiplos terabytes.

Você já viu esse cenário no monitoramento: a CPU do servidor de banco de dados está em 40% de uso, mas as queries estão lentas e o I/O de disco está saturado ou, pior, a latência de espera por memória está nas alturas. Para nós, DBAs e arquitetos de infraestrutura, não há frustração maior do que ter poder de processamento disponível e não conseguir entregar os dados para os núcleos a tempo.

O gargalo não é mais o disco giratório e, em muitos casos, nem mesmo o SSD NVMe convencional. O problema é a física da placa-mãe e a limitação dos canais DDR. Estamos entrando na era do CXL 3.1 (Compute Express Link), uma tecnologia que promete transformar o barramento PCIe em uma extensão direta do mapa de memória da CPU. Para quem gerencia grandes volumes de dados (VLDBs) e in-memory databases como SAP HANA, Redis ou instâncias massivas de SQL Server, isso muda a regra do jogo de alocação de recursos.

Resumo em 30 segundos

- O Muro da Memória: CPUs modernas escalaram em núcleos muito mais rápido do que a capacidade e largura de banda dos canais de memória DDR5 conseguem acompanhar.

- Latência vs. Throughput: O CXL permite adicionar memória via slot PCIe com latência próxima à da DRAM nativa, algo impossível com SSDs NVMe, que operam em blocos e não em bytes.

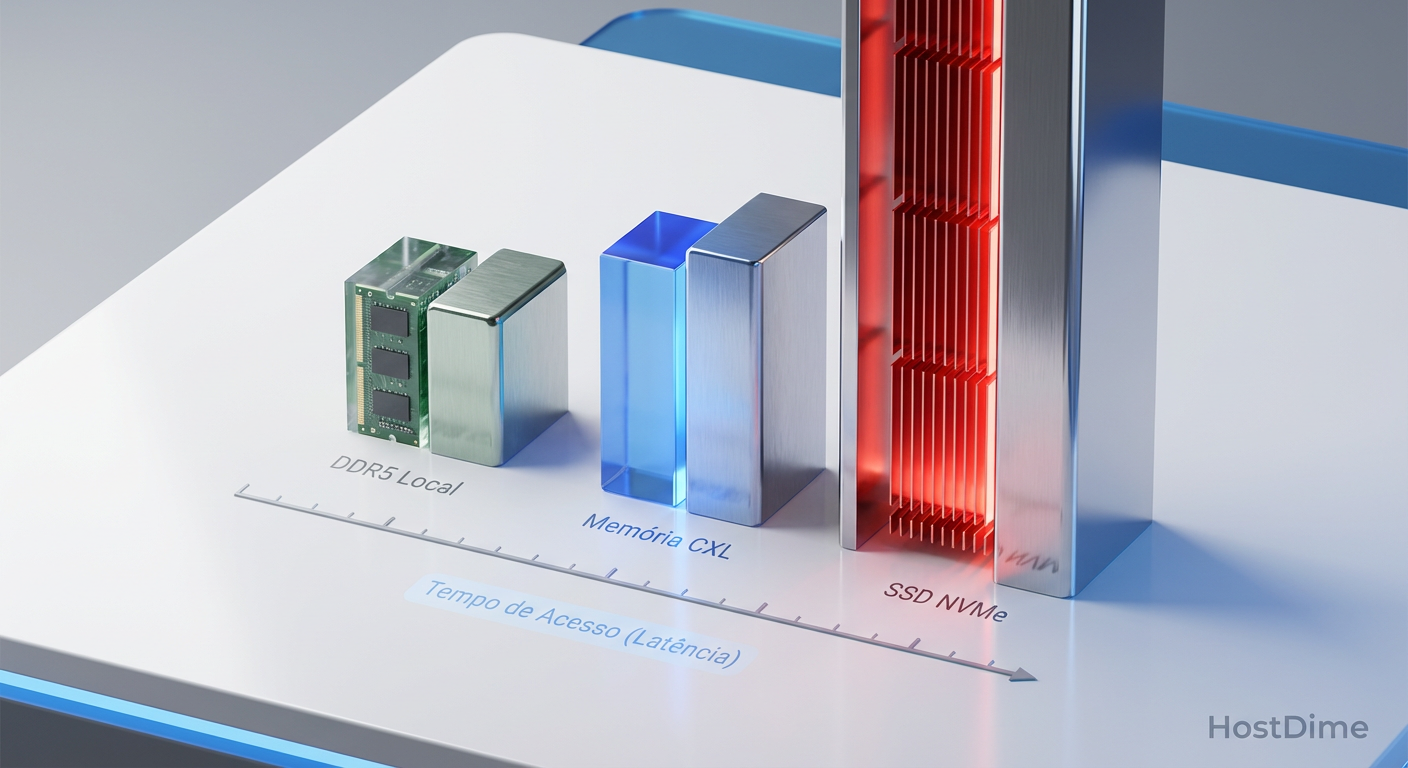

- Desagregação Real: Com o CXL 3.1, podemos criar "pools" de memória compartilhada entre vários servidores, eliminando o desperdício de RAM presa em servidores ociosos (stranded memory).

O paradoxo da CPU ociosa em grandes volumes de dados

A Lei de Moore continua empurrando a densidade de transistores, nos dando processadores EPYC e Xeon com 64, 96 ou até 128 núcleos. No entanto, a arquitetura de memória não acompanhou essa densidade. Um servidor moderno típico tem 12 canais de memória. Se você precisa de alta capacidade, é forçado a usar DIMMs de alta densidade (e alto custo) ou reduzir a frequência da memória para popular dois DIMMs por canal (2DPC).

Para um DBA, isso cria o "paradoxo da CPU ociosa". O processador passa milhares de ciclos de clock esperando que os dados sejam trazidos da memória principal para os caches L1/L2/L3. Se os dados não cabem na RAM, o sistema operacional faz page out para o armazenamento.

⚠️ Perigo: Não confunda latência de armazenamento com latência de memória. Um SSD NVMe Gen5 topo de linha tem uma latência de leitura na casa dos 10 a 60 microssegundos. A memória DRAM opera em nanossegundos. Para uma CPU de 4GHz, buscar dados no SSD é como esperar anos por uma carta, enquanto buscar na RAM é como pegar um livro na estante.

Quando o working set (o conjunto de dados ativos) do seu banco de dados excede a RAM física instalada, a performance cai de um penhasco. Até hoje, a única solução era "scale-up": comprar um servidor maior, com mais slots DIMM, custando uma fortuna.

Fig. 1: A quebra do paradigma de acoplamento rígido entre CPU e Memória.

Fig. 1: A quebra do paradigma de acoplamento rígido entre CPU e Memória.

Limitações físicas dos canais DDR5 e o abismo de latência

A engenharia de placas-mãe atingiu um limite físico. Traçar centenas de trilhas de sinal paralelo da CPU até os slots de memória requer uma integridade de sinal imaculada. É por isso que não vemos servidores com 40 slots de memória DDR5; a interferência e a degradação do sinal tornam isso inviável sem reduzir drasticamente a velocidade.

Aqui entra a distinção crítica que muitos generalistas de TI ignoram: Acesso Aleatório a Byte vs. Acesso a Bloco.

Bancos de dados relacionais e NoSQL operam manipulando estruturas de dados complexas (B-Trees, Hash Maps) que exigem acesso granular a endereços de memória específicos. O protocolo DDR foi feito para isso. O protocolo NVMe, por mais rápido que seja, foi desenhado para armazenamento em bloco (4KB, 8KB, etc.).

Por que o tiering para NVMe falha em cargas transacionais

Muitas soluções de software tentaram resolver a falta de RAM usando SSDs NVMe como uma extensão da memória (Memory Tiering ou Swap inteligente). Embora funcione para cold data, falha miseravelmente em cargas transacionais pesadas (OLTP).

O motivo é a granularidade. Para ler 64 bytes de um registro de cliente em um SSD, o sistema precisa:

Gerar uma interrupção ou fazer polling.

Ler um bloco inteiro de 4KB (desperdício de largura de banda).

Copiar isso para a DRAM.

A CPU finalmente lê o dado.

Isso destrói o throughput de transações por segundo (TPS). O CXL resolve isso permitindo que a CPU acesse a memória conectada via PCIe usando instruções de load/store (semântica de memória), e não instruções de I/O.

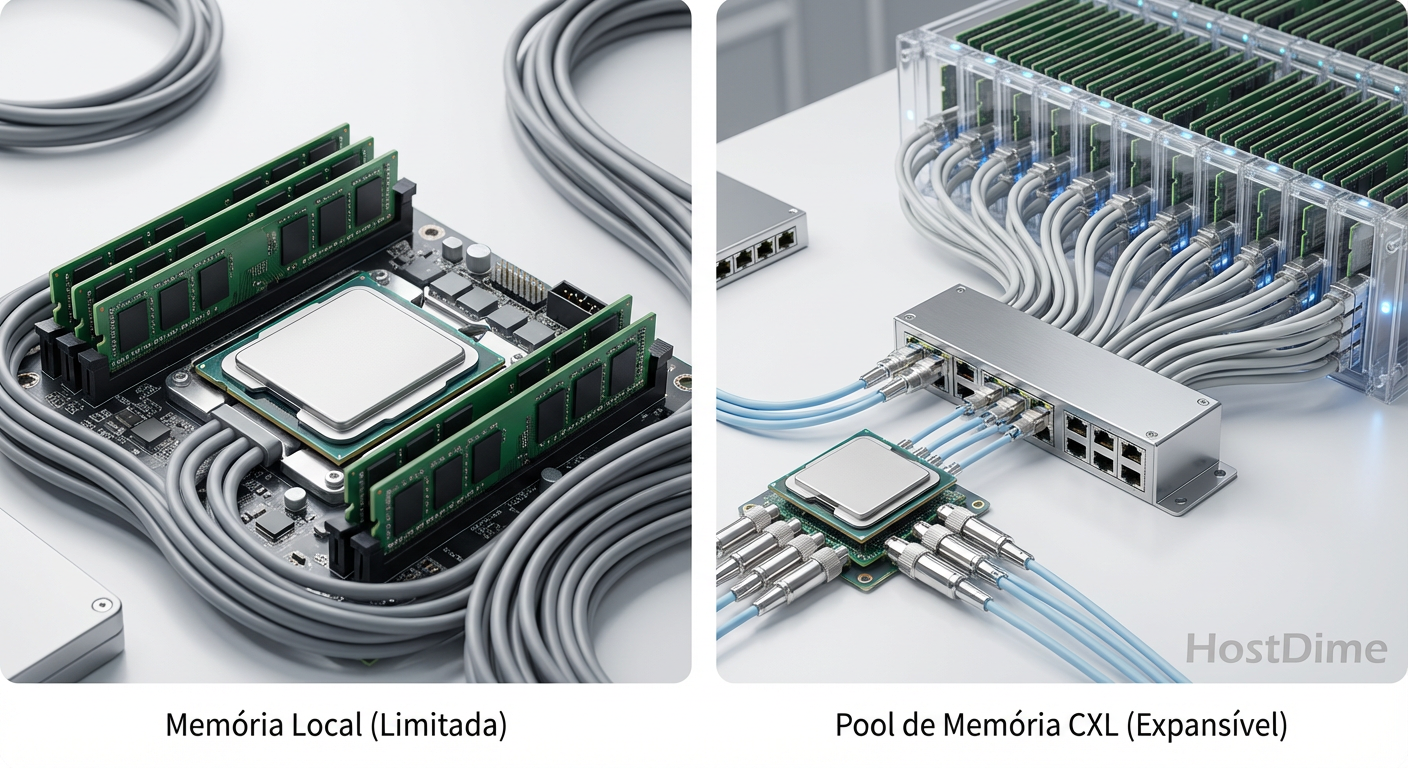

Fig. 2: O abismo de latência: Por que o CXL é memória e o SSD é armazenamento.

Fig. 2: O abismo de latência: Por que o CXL é memória e o SSD é armazenamento.

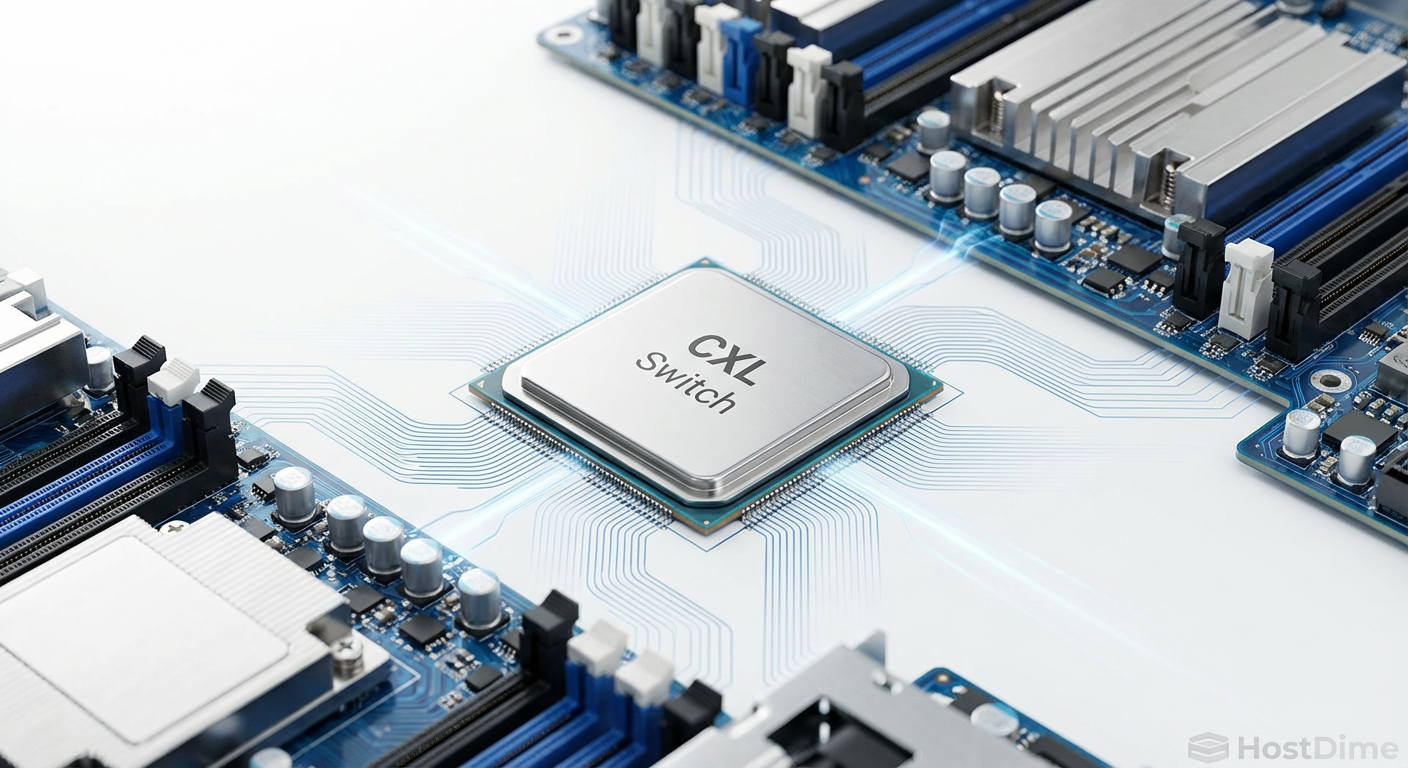

Arquitetura CXL 3.1 e a democratização da memória via PCIe

O Compute Express Link (CXL) é um protocolo aberto construído sobre a camada física do PCIe. A versão 3.0 e a atualização 3.1 (baseadas no PCIe 6.0) trazem a largura de banda e os recursos de fabric necessários para que isso funcione em escala de Data Center.

O CXL opera em três sub-protocolos, mas para nós, arquitetos de dados, o CXL.mem é o que importa. Ele permite que um dispositivo (uma placa com chips DRAM, parecida com uma GPU ou SSD) seja mapeado diretamente no espaço de endereçamento físico do processador.

O que muda com o CXL 3.1?

Enquanto o CXL 1.1/2.0 focava na expansão de memória dentro de um único chassi, o CXL 3.1 habilita o verdadeiro Memory Pooling e Fabric.

Largura de Banda Dobrada: Usando a sinalização PAM4 do PCIe 6.0, o CXL 3.0+ entrega até 64 GT/s. Isso reduz a penalidade de latência de usar o barramento serial em vez do paralelo (DDR).

Global Fabric Attached Memory (GFAM): O CXL 3.1 permite criar um "appliance de memória". Imagine um chassi cheio de módulos de memória que não tem CPU. Vários servidores de banco de dados podem se conectar a esse chassi via switch CXL e alocar 1TB, 2TB ou 10TB de RAM sob demanda.

Coerência de Cache: O hardware garante que, se o Servidor A escrever em um endereço de memória compartilhado, o Servidor B saberá que seu cache está inválido. Isso é vital para clusters de banco de dados ativo-ativo (como Oracle RAC) sem o overhead brutal de software.

💡 Dica Pro: Em uma arquitetura NUMA (Non-Uniform Memory Access) com CXL, a memória CXL aparecerá como um "NUMA Node" sem CPU. Configure seu banco de dados (ex: SQL Server ou PostgreSQL) para entender essa topologia. Dados "mornos" devem residir preferencialmente no nó CXL, deixando a DRAM local (DDR5 direta) para os dados mais quentes e buffers de log.

Comparativo: DDR5 Nativa vs. CXL vs. NVMe

Para situar onde o CXL se encaixa na hierarquia de armazenamento, analise a tabela abaixo focada em latência e acesso:

| Característica | DDR5 (Local) | CXL 3.1 (Memória) | NVMe Gen5 (Armazenamento) |

|---|---|---|---|

| Latência Típica | ~70-100 ns | ~170-250 ns | ~10.000-60.000 ns |

| Acesso | Byte-addressable (Load/Store) | Byte-addressable (Load/Store) | Block-addressable (I/O) |

| Protocolo | DDR Paralelo | CXL.mem (sobre PCIe) | NVMe |

| Persistência | Volátil | Volátil (geralmente) | Persistente |

| Custo/GB | Alto | Médio (permite mídia mais barata) | Baixo |

Note que a latência do CXL é maior que a da memória local (cerca de um "hop" NUMA de distância), mas é ordens de magnitude menor que a do NVMe. Para um banco de dados, essa diferença de ~100ns é aceitável para 80% dos dados que não cabem na memória principal.

Ganhos de TCO e latência em topologias de memória desagregada

O maior argumento para a adoção do CXL 3.1 não é apenas performance, é Custo Total de Propriedade (TCO).

Em um cluster de virtualização ou de banco de dados tradicional, provisionamos servidores com o máximo de RAM para suportar o "pior cenário". O resultado é que, em média, 40-50% da DRAM no Data Center fica ociosa ("Stranded Memory"). Você pagou por ela, ela consome energia (refresh cycles), mas não armazena dados úteis.

Com a topologia de Fabric do CXL 3.1, podemos reduzir a RAM instalada diretamente na placa-mãe (cortando custos de CAPEX drasticamente) e ter um pool centralizado de memória CXL.

Cenário Prático: Consolidação de Banco de Dados

Imagine consolidar 20 instâncias de SQL Server. Em vez de colocar 1TB de RAM em cada host físico, você coloca 256GB. Quando uma instância específica precisa rodar um relatório mensal pesado de OLAP, o orquestrador aloca dinamicamente mais 500GB do pool CXL para aquele host. Terminada a query, a memória é devolvida ao pool.

Isso elimina a necessidade de over-provisioning massivo. Além disso, o CXL permite o uso de mídias de memória diferentes atrás do controlador. Você pode ter módulos CXL que usam DDR4 (mais barato) internamente, ou até futuras memórias de classe de armazenamento (SCM), apresentando tudo como "Memória do Sistema" para o SO.

Fig. 3: O Switch CXL atuando como o coração da nova topologia de fabric no Data Center.

Fig. 3: O Switch CXL atuando como o coração da nova topologia de fabric no Data Center.

Previsão para a Arquitetura de Dados

O CXL 3.1 não é apenas uma nova versão de especificação; é o fim da distinção rígida entre "computação" e "memória" como componentes soldados na mesma caixa. Para o arquiteto de workloads, isso significa que o design de bancos de dados de alta performance deixará de ser limitado pelos slots DIMM do servidor.

A recomendação técnica para os próximos ciclos de renovação de hardware (2025-2027) é clara: exija suporte a CXL nas suas plataformas de servidor (Gen5/Gen6 PCIe). Mesmo que você não compre os módulos de memória CXL no dia 1, a capacidade de expandir a RAM sem trocar o servidor ou recorrer ao swap em disco será o diferencial entre uma migração de dados tranquila e um gargalo de performance insuperável.

Preparem seus buffer pools. A hierarquia de memória acabou de ganhar um novo degrau, e ele é rápido.

Referências & Leitura Complementar

Para aprofundamento técnico real, ignore o marketing e vá direto às especificações e análises de engenharia:

Compute Express Link™ (CXL™) 3.1 Specification: Documento oficial do Consórcio CXL detalhando as melhorias de fabric e coerência sobre o 3.0.

SNIA (Storage Networking Industry Association): "Persistent Memory and CXL" – Whitepapers técnicos sobre como o modelo de programação de memória persistente se adapta ao barramento CXL.

JEDEC DDR5 SDRAM Standard (JESD79-5): Para entender as limitações de latência e largura de banda que tornam o CXL necessário.

PCI-SIG PCI Express 6.0 Specification: A base física (PHY) sobre a qual o CXL 3.1 opera, detalhando a sinalização PAM4 e correção de erro (FEC).

Perguntas Frequentes (FAQ)

1. O CXL substitui a memória RAM DDR5 tradicional? Não. A memória conectada diretamente à CPU (Near Memory) sempre terá a menor latência. O CXL atua como uma camada de "Far Memory", ideal para expandir capacidade sem a penalidade de desempenho do armazenamento em disco.

2. Preciso alterar meu código SQL ou a aplicação para usar CXL? Geralmente não. O hardware e o Sistema Operacional apresentam a memória CXL como parte do espaço de endereçamento físico. No entanto, aplicações "NUMA-aware" (conscientes da topologia de memória) terão melhor desempenho se configuradas para priorizar a memória local para threads críticos.

3. A memória CXL é persistente (não volátil)? O protocolo CXL suporta tanto memória volátil (DRAM) quanto persistente. Depende do dispositivo conectado. A maioria das implementações iniciais (Type 3 devices) foca em expansão de capacidade volátil, mas o potencial para Storage Class Memory (SCM) persistente é nativo da especificação.

4. Qual a diferença entre CXL 2.0 e 3.1? O CXL 2.0 introduziu o switching básico. O CXL 3.0 e 3.1 (baseados em PCIe 6.0) dobram a largura de banda e introduzem recursos avançados de fabric, permitindo comunicação peer-to-peer entre dispositivos e compartilhamento de memória global entre múltiplos hosts sem passar pela CPU raiz.

Roberto Lemos

Arquiteto de Workloads

"Projeto infraestrutura onde o perfil de I/O dita as regras. Sei que a latência do acesso aleatório de um banco difere da vazão sequencial de vídeos. Mapeio o hardware exato para cada aplicação."