O fim da memória isolada: desagregação via CXL 3.1 em workloads de IA

Análise técnica sobre como o CXL 3.1 elimina o gargalo de memória em clusters de IA, superando as limitações de HBM3e e DDR5 com pools compartilhados de baixa latência.

O fim da memória isolada: desagregação via CXL 3.1 em workloads de IA

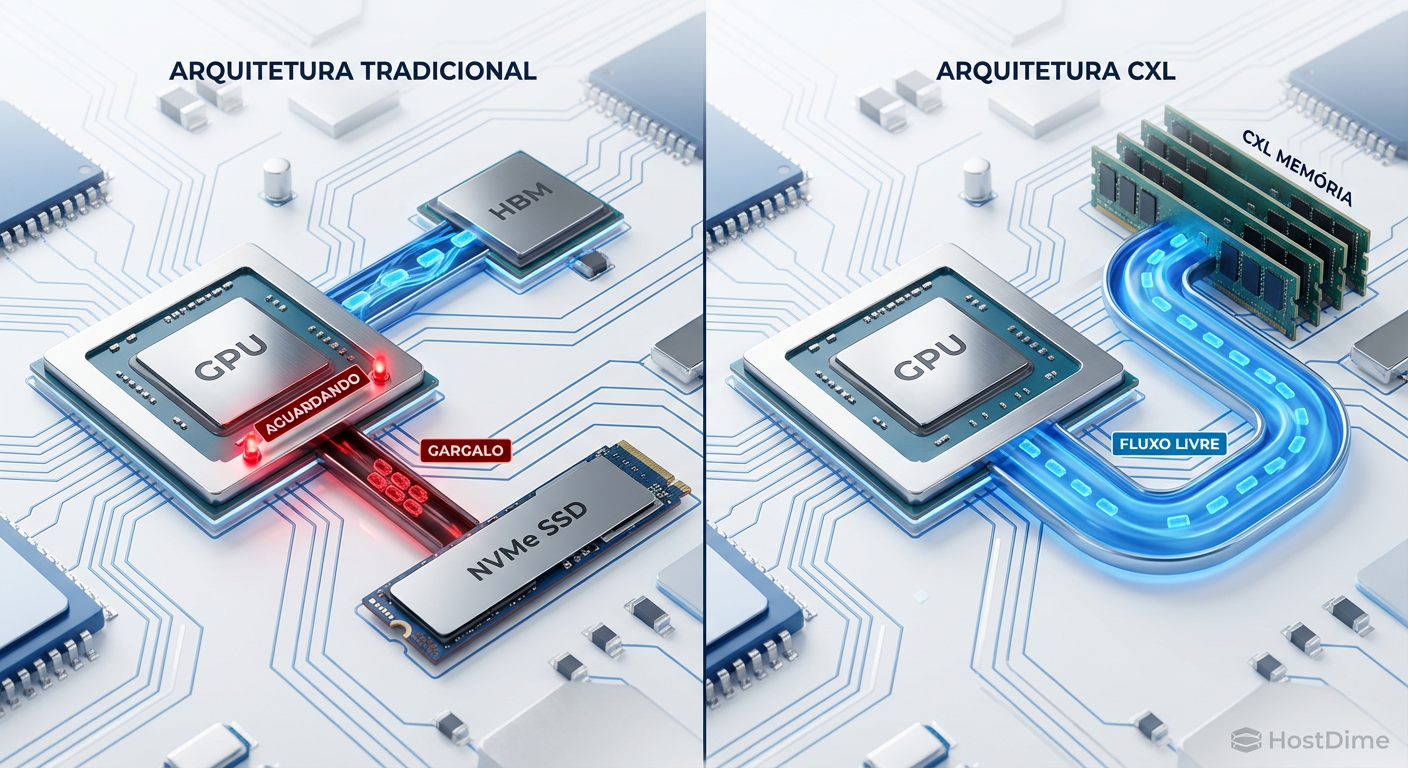

Se você gerencia bancos de dados de alta performance ou clusters de treinamento de IA, sabe que o gargalo raramente é o poder de computação bruto. O problema é a fome. As GPUs modernas, como as baseadas na arquitetura Blackwell ou Hopper, são motores vorazes que passam tempo demais esperando o "combustível" chegar. Historicamente, tratamos a memória RAM como um recurso privado, soldado ao lado da CPU, inacessível aos vizinhos. Essa arquitetura monolítica está morta para a escala de exabytes.

A indústria de armazenamento e infraestrutura vive um ponto de inflexão com a chegada do CXL (Compute Express Link) 3.1. Não estamos falando apenas de um barramento mais rápido; estamos falando da dissolução das fronteiras físicas do servidor. Para um arquiteto de workloads, isso significa que a memória deixa de ser um componente estático para se tornar um recurso dinâmico, roteável e compartilhado, tal qual um LUN em uma SAN, mas com semântica de memória e latência de nanosegundos.

Resumo em 30 segundos

- O problema da HBM: A memória de alta largura de banda (HBM) nas GPUs é escassa e cara. Quando ela enche, o spillover para NVMe mata a performance.

- CXL 3.1 como Fabric: Diferente das versões anteriores, o CXL 3.1 permite criar pools de memória compartilhada entre múltiplos hosts, eliminando o desperdício de RAM presa em servidores ociosos.

- Latência viável: Com penalidades na casa de 20-40ns sobre PCIe 6.0, a memória via CXL atua como um "Tier 2" perfeito, ordens de magnitude mais rápida que o SSD mais veloz do mercado.

Ociosidade de GPU e o custo oculto do carregamento de tensores

Vamos ser diretos: uma GPU com 50% de utilização não é um recurso "disponível", é um prejuízo ativo. Em workloads de Large Language Models (LLMs) ou Recommendation Systems (DLRM), o tamanho do modelo frequentemente excede a capacidade da HBM (High Bandwidth Memory) local.

Quando o dataset ou os parâmetros do modelo não cabem na VRAM, o sistema tradicionalmente recorre à memória do sistema (DDR5) via CPU, ou pior, faz swapping para discos NVMe locais.

Aqui reside o problema físico. Um SSD NVMe Enterprise de ponta, conectado via PCIe 5.0, entrega algo em torno de 14 GB/s de throughput e latência na casa dos microssegundos (µs). Para um banco de dados transacional, isso é excelente. Para uma GPU que mastiga terabytes por segundo, é como tentar encher uma piscina olímpica usando um canudo.

O resultado é a "inanição de dados" (data starvation). A GPU para de calcular e espera o I/O. Você pagou por um supercomputador, mas a latência do armazenamento o transformou em um aquecedor de ambiente muito caro.

Figura: Comparativo de fluxo de dados: O gargalo do NVMe tradicional vs. a largura de banda expandida via CXL Memory Pool.

Figura: Comparativo de fluxo de dados: O gargalo do NVMe tradicional vs. a largura de banda expandida via CXL Memory Pool.

A falácia da escala horizontal para resolver déficit de memória

Até recentemente, se você precisasse de mais memória para um modelo de IA, a única solução era adicionar mais nós de computação. Se um servidor tem 2TB de RAM e você precisa de 4TB para manter o modelo em memória, você comprava um segundo servidor.

Isso cria dois problemas graves de TCO (Total Cost of Ownership):

Recursos Presos (Stranded Resources): Você comprou o segundo servidor pela memória, mas as CPUs e GPUs dele podem ficar ociosas se o gargalo for apenas capacidade de armazenamento volátil.

Complexidade de Sharding: Distribuir o modelo entre nós via rede (InfiniBand/Ethernet) introduz latência de rede e complexidade de software (MPI, NCCL).

O CXL 3.1 resolve isso desacoplando a memória da CPU. A memória não precisa mais "pertencer" a uma placa-mãe específica.

Entendendo o CXL 3.1 e PCIe 6.0

O Compute Express Link (CXL) é um protocolo aberto construído sobre a camada física do PCIe. Enquanto o CXL 1.1 e 2.0 focavam na expansão de memória para um único host (como um "pen drive de RAM"), o CXL 3.1, operando sobre a velocidade do PCIe 6.0 (64 GT/s), introduz o conceito de Fabric.

💡 Dica Pro: Não confunda CXL com RDMA. O RDMA move dados de memória para memória via rede (cópia). O CXL permite que a CPU/GPU acesse o endereço de memória remota diretamente com instruções de load/store (acesso semântico), sem intervenção do SO para mover pacotes.

Tecido de memória: roteamento e acesso direto

A grande inovação do CXL 3.1 é o suporte a multi-level switching e topologias de fabric. Isso permite a criação de Memory Appliances — caixas que contêm apenas módulos de memória (DDR5 ou futura DDR6) e controladores CXL.

Esses appliances se conectam a um switch CXL, que por sua vez se conecta a múltiplos servidores (Hosts).

Global Integrated Memory (GIM)

Em um ambiente de banco de dados distribuído ou treinamento de IA, a coerência de cache é o pesadelo do arquiteto. O CXL 3.1 introduz melhorias no protocolo de coerência, permitindo que múltiplos hosts acessem e modifiquem a mesma região de memória no appliance.

Imagine um cluster Oracle RAC ou um sistema de arquivos distribuído onde o "disco compartilhado" é, na verdade, memória RAM volátil. A latência de bloqueio e coordenação cai drasticamente.

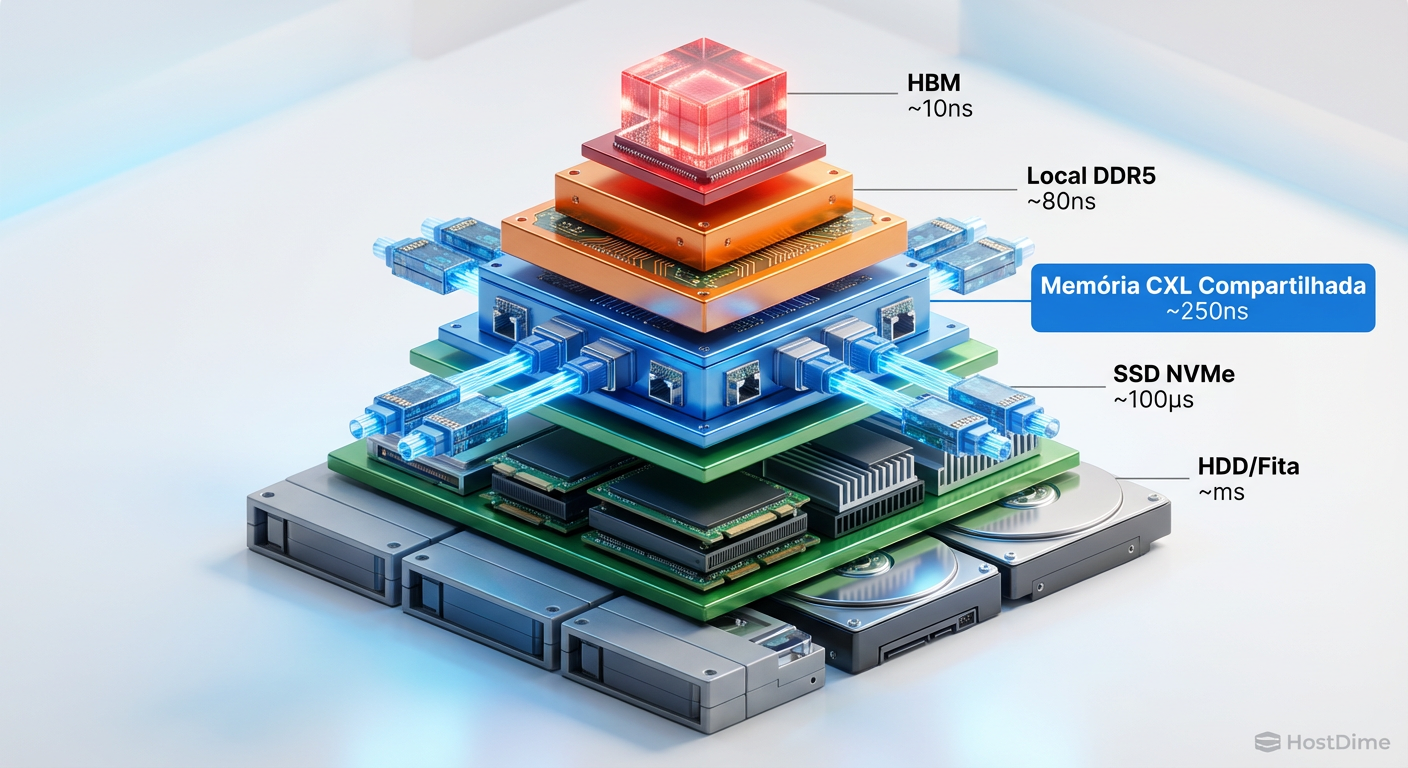

Tabela Comparativa: Hierarquia de Armazenamento na Era CXL

Para situar onde o CXL se encaixa, precisamos olhar para a latência e a capacidade.

| Tecnologia | Latência Típica | Largura de Banda (por linha/canal) | Custo/GB | Caso de Uso Principal |

|---|---|---|---|---|

| HBM3e (GPU) | < 10 ns | ~1.2 TB/s (por stack) | Extremo | Dados "quentes" imediatos (Tensores ativos). |

| DDR5 (Local) | ~80-100 ns | ~32-48 GB/s | Alto | Sistema Operacional, Apps sensíveis à latência. |

| CXL 3.1 (Remoto) | ~120-150 ns | ~64 GB/s (x4 PCIe 6.0) | Médio | Expansão de capacidade, In-Memory DBs, Checkpoints de IA. |

| NVMe (PCIe 5.0) | ~10.000 ns (10µs) | ~14 GB/s | Baixo | Armazenamento persistente, Cold Data. |

| HDD (SAS) | ~5.000.000 ns | ~0.25 GB/s | Mínimo | Arquivamento, Data Lakes massivos. |

Note o salto brutal entre CXL e NVMe. O CXL preenche o abismo de desempenho que existia entre a RAM local e o SSD mais rápido.

Figura: A nova pirâmide de hierarquia de memória: O CXL preenche o abismo entre DDR e NVMe.

Figura: A nova pirâmide de hierarquia de memória: O CXL preenche o abismo entre DDR e NVMe.

Impacto arquitetural em clusters de IA

Ao desenhar a infraestrutura para treinamento de modelos massivos, a desagregação via CXL 3.1 altera as regras do jogo de três formas principais:

1. Checkpointing Instantâneo

O treinamento de LLMs pode levar semanas. Falhas de hardware são estatisticamente garantidas. O processo de checkpointing (salvar o estado do modelo no disco) é uma operação de I/O pesada que pausa o treinamento. Com CXL, o checkpoint pode ser escrito em uma região de memória remota persistente (ou protegida por bateria) na velocidade da RAM. O tempo de pausa cai de minutos para segundos.

2. Inferência de Grandes Modelos (Inference at Scale)

Para inferência, muitas vezes o modelo não precisa ser treinado, apenas lido. Com CXL, podemos carregar um modelo de 1TB em um Memory Appliance e permitir que 4, 8 ou 16 servidores de inferência leiam esse mesmo modelo diretamente da memória compartilhada (Zero-Copy), sem precisar duplicar os dados na RAM local de cada servidor. Isso reduz drasticamente o custo de hardware para inferência.

3. Tiering de Memória Transparente

Softwares de gerenciamento de memória (como o Meta's TPP - Transparent Page Placement) podem mover páginas frias da HBM para a DDR local, e da DDR local para o CXL, de forma invisível para a aplicação. O CXL atua como uma área de swap ultra-rápida. A aplicação "pensa" que tem 10TB de RAM local, quando na verdade tem 512GB locais e 9.5TB via CXL.

⚠️ Perigo: A latência do CXL, embora baixa, não é idêntica à da memória local (NUMA node 0). Aplicações que não são NUMA-aware podem sofrer degradação de performance se acessarem memória CXL aleatoriamente achando que é local. O pinning de processos e a gestão correta de pages são vitais.

Figura: Arquitetura física de rack: Compute Nodes acessando um JBOM (Just a Bunch of Memory) via CXL Fabric.

Figura: Arquitetura física de rack: Compute Nodes acessando um JBOM (Just a Bunch of Memory) via CXL Fabric.

O veredito arquitetural

A era da memória isolada é uma relíquia de um tempo em que 64GB de RAM eram considerados "muito". Para workloads de IA e Big Data modernos, a memória precisa ser fluida. O CXL 3.1 sobre PCIe 6.0 não é apenas uma evolução de velocidade; é uma mudança de topologia.

Para nós, arquitetos e DBAs, isso significa que o planejamento de capacidade muda de "quantos pentes de memória cabem neste slot?" para "qual a largura de banda do meu fabric de memória?". A desagregação permite que compremos computação e memória em ciclos diferentes, otimizando o TCO e reduzindo o desperdício de silício ocioso.

Prepare seus kernels e revise suas políticas de NUMA. O banco de dados do futuro não mora mais apenas dentro do servidor; ele mora no fabric.

Referências & Leitura Complementar

Para aprofundamento técnico real, recomendo a leitura das especificações originais e whitepapers das entidades normativas:

CXL Consortium: Compute Express Link 3.1 Specification (Lançado em fins de 2023, atualizado em 2024). Define os protocolos de coerência e fabric.

PCI-SIG: PCI Express 6.0 Specification. A base física necessária para a largura de banda do CXL 3.0+.

SNIA (Storage Networking Industry Association): Smart Data Transfer Interface (SDXI). Relevante para entender como a movimentação de memória offloadada interage com CXL.

JEDEC: DDR5 SDRAM Standard (JESD79-5). Entender a memória base é crucial para entender o que está sendo transportado.

FAQ: Perguntas Frequentes sobre CXL e Storage

Qual a diferença crítica entre CXL 2.0 e CXL 3.1 para IA?

Enquanto o CXL 2.0 foca em expansão ponto-a-ponto e switching simples, o CXL 3.1 introduz capacidades reais de fabric, permitindo comunicação Peer-to-Peer (P2P) direta entre dispositivos (ex: GPU acessando memória remota sem passar pela CPU host) e Global Integrated Memory (GIM) para coerência entre múltiplos hosts.O CXL 3.1 substitui a memória HBM nas GPUs?

Não. A HBM (High Bandwidth Memory) continua sendo a camada de ultra-velocidade (TB/s) para dados imediatos. O CXL 3.1 atua como uma camada intermediária de capacidade massiva e latência próxima à DDR (nanosegundos), evitando que o sistema precise buscar dados em discos NVMe (microssegundos) quando a HBM enche.Qual é a penalidade de latência ao usar memória via CXL?

Em implementações otimizadas sobre PCIe 6.0, a penalidade é de aproximadamente 20 a 40 nanosegundos adicionais em comparação à memória DDR5 local. Isso é ordens de magnitude mais rápido que qualquer SSD NVMe, tornando-o viável para expansão de memória ativa.

Roberto Lemos

Arquiteto de Workloads

"Projeto infraestrutura onde o perfil de I/O dita as regras. Sei que a latência do acesso aleatório de um banco difere da vazão sequencial de vídeos. Mapeio o hardware exato para cada aplicação."