PCIe switch vs bifurcação: o dilema entre latência e segurança em backplanes NVMe

Descubra se você deve usar chips PLX ou bifurcação nativa para seus arrays NVMe. Analisamos latência, custo e isolamento de falhas para servidores e workstations.

Você montou um servidor de armazenamento de alta performance ou uma workstation extrema. Comprou os melhores SSDs NVMe do mercado, mas agora enfrenta um problema físico: sua CPU tem um número limitado de pistas PCIe (lanes), e você quer conectar mais drives do que o processador suporta nativamente.

É aqui que a arquitetura do backplane se torna crítica. Você tem dois caminhos: a simplicidade bruta da bifurcação PCIe ou a inteligência complexa de um switch PCIe (frequentemente chamados de chips PLX ou Broadcom).

Essa escolha não é apenas sobre "funcionar". Ela define se o seu sistema terá a latência de um carro de Fórmula 1 ou a resiliência de um tanque de guerra. Vamos dissecar essa infraestrutura invisível que dita o comportamento do seu storage.

Resumo em 30 segundos

- Bifurcação: Divide as pistas da CPU eletricamente (ex: x16 vira quatro x4). É a opção mais barata e de menor latência, ideal para workstations e HFT (High-Frequency Trading), mas carece de proteção contra falhas.

- Switch PCIe: Funciona como um switch de rede, permitindo conectar muitos SSDs a poucas pistas da CPU (oversubscription). Adiciona custo e latência, mas garante hot-swap seguro e isolamento de erros.

- O Veredito: Use bifurcação para velocidade pura em ambientes controlados. Use switches para servidores de missão crítica onde a estabilidade do barramento é inegociável.

A rota dos dados: CPU ao SSD

Para entender a briga, precisamos olhar para o caminho físico. O protocolo NVMe (Non-Volatile Memory Express) conversa diretamente com a CPU através do barramento PCIe. Em um cenário ideal, cada SSD teria suas próprias 4 pistas dedicadas (x4) indo direto ao processador.

O problema é a matemática. Uma CPU moderna de servidor (como AMD EPYC ou Intel Xeon Scalable) oferece entre 64 a 128 pistas PCIe. Parece muito, mas adicione algumas GPUs, placas de rede de 100GbE e controladoras RAID, e de repente você não tem pistas suficientes para aquele backplane frontal de 24 baias U.2 ou E1.S.

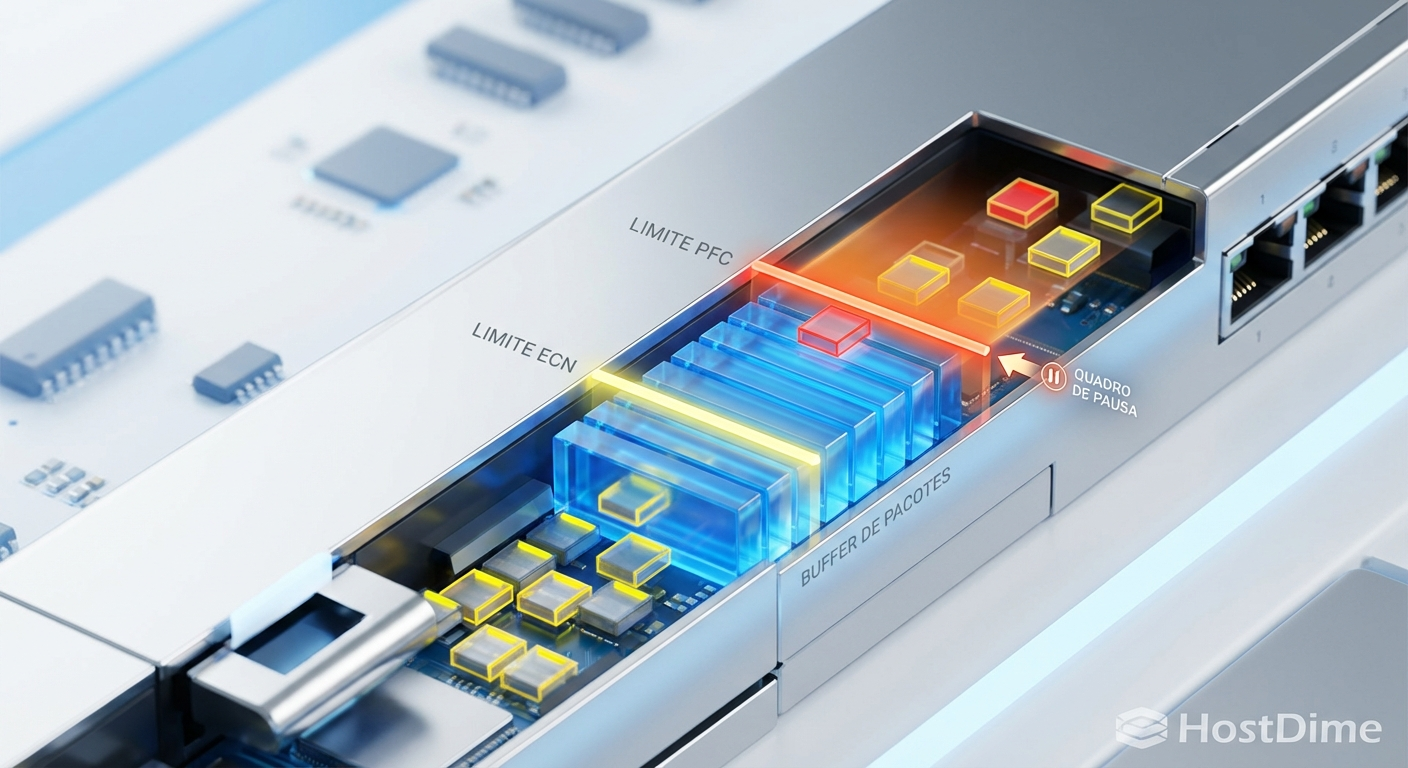

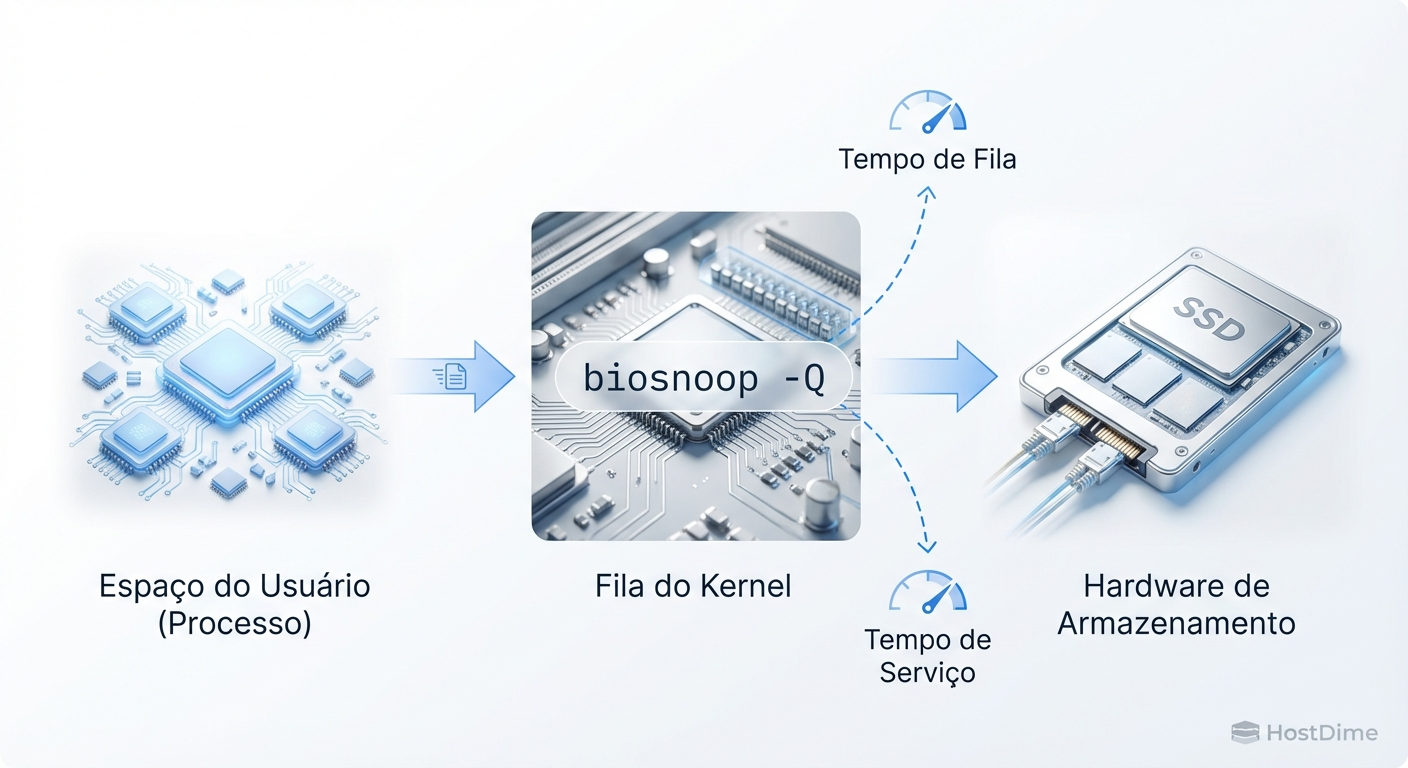

Figura: Comparativo visual: conexão direta via bifurcação versus conexão intermediada por switch.

Figura: Comparativo visual: conexão direta via bifurcação versus conexão intermediada por switch.

Bifurcação: a arte de dividir fios

A bifurcação PCIe não é mágica; é uma configuração elétrica gerenciada pela BIOS/UEFI. Imagine um slot x16 físico. Normalmente, ele espera um único dispositivo x16. Ao ativar a bifurcação (ex: x4x4x4x4), você diz à CPU: "Não trate isso como uma estrada larga, trate como quatro estradas estreitas independentes".

Vantagens da bifurcação

A maior vantagem é a transparência. Não há chip intermediário processando pacotes. O sinal elétrico vai do pino da CPU ao pino do SSD.

Custo Zero: Não requer chips caros na placa-mãe ou na riser card.

Latência Mínima: Não há "hop" (salto) adicional.

Onde a bifurcação falha

A dependência é total do suporte da placa-mãe. Se a BIOS não permitir dividir um slot x16 em x4x4, você não pode usar uma placa riser passiva para ligar 4 SSDs M.2 ou U.2; apenas o primeiro drive será reconhecido. Além disso, a bifurcação é rígida. Você não pode ligar 5 drives em um slot x16, pois a matemática não fecha.

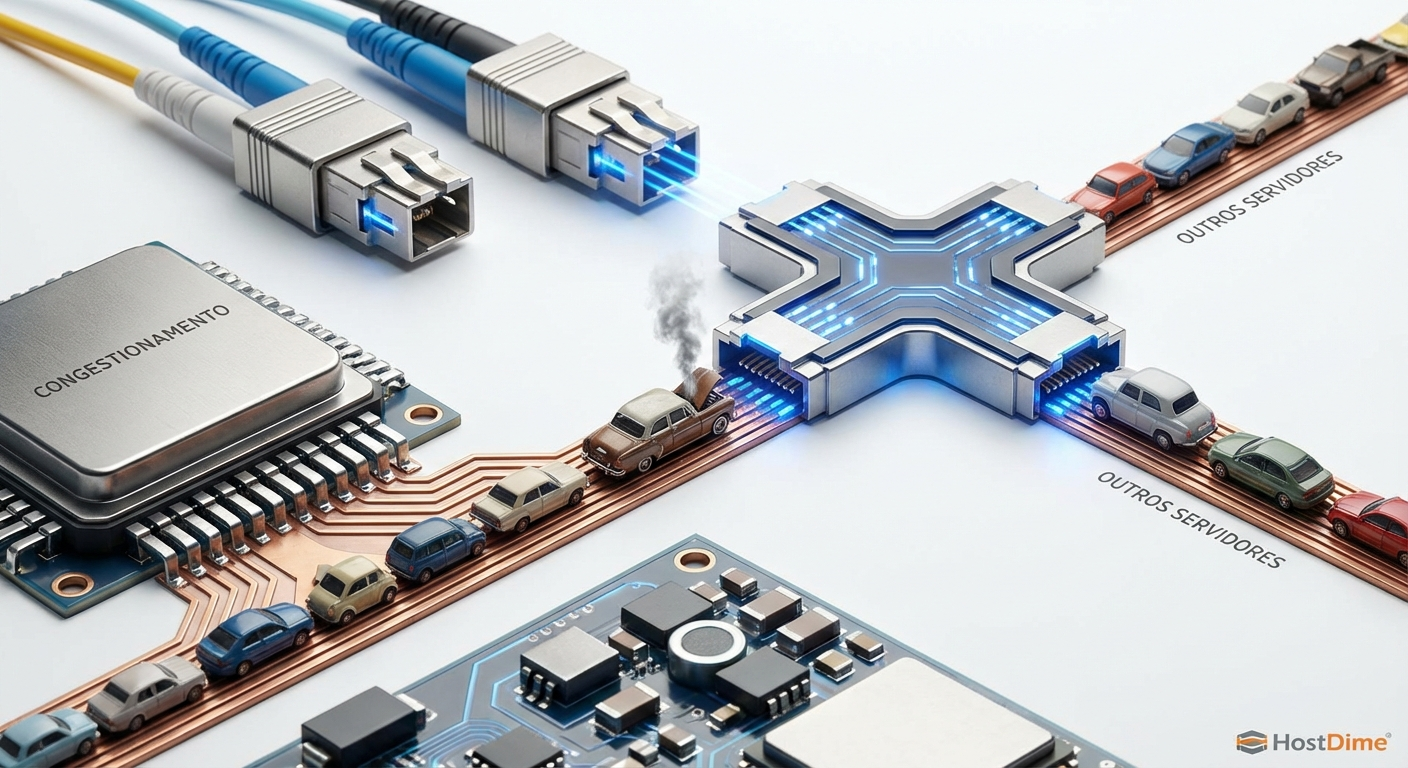

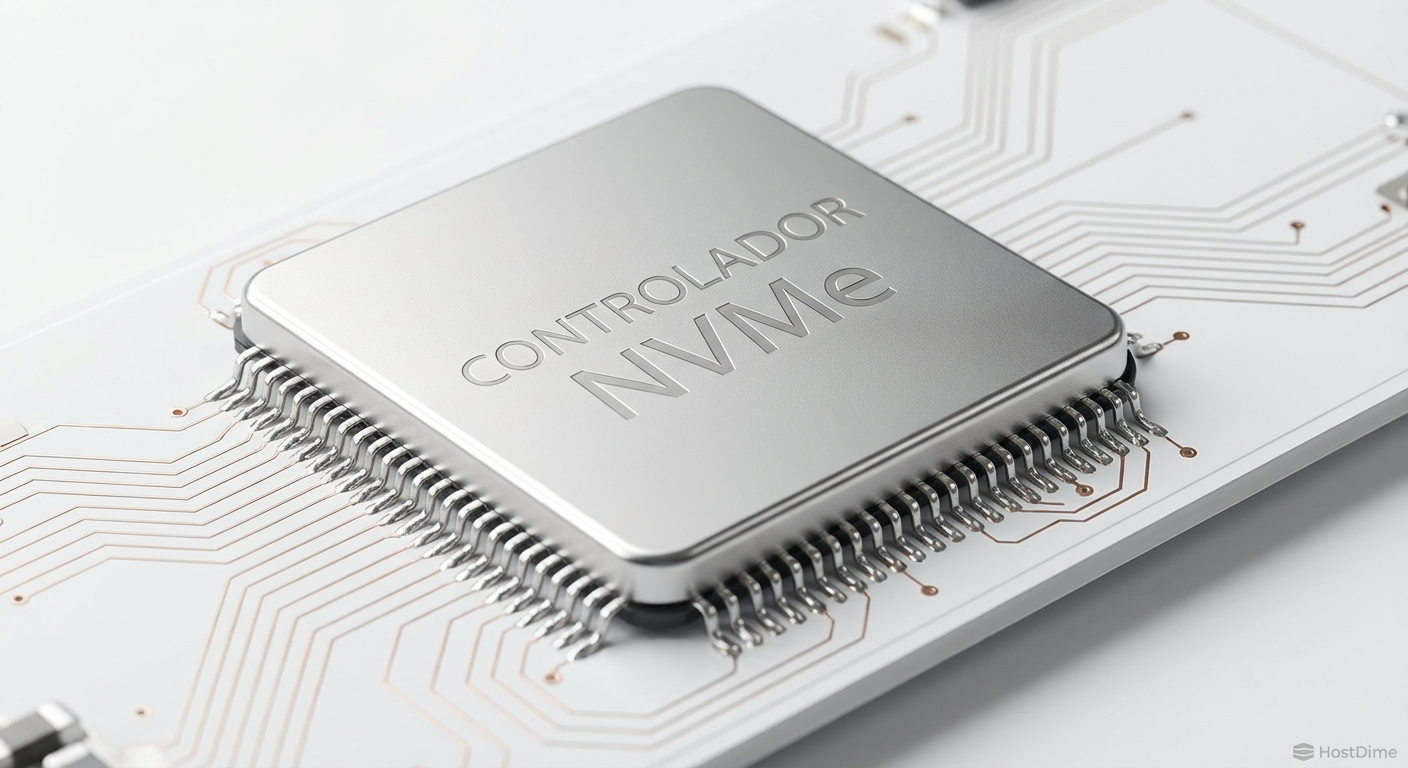

Switches PCIe: o guarda de trânsito inteligente

Um switch PCIe (comumente fabricado pela Broadcom, Microchip ou, historicamente, PLX) é um computador em miniatura dedicado a rotear tráfego. Ele recebe pacotes de dados da CPU e decide para qual porta de saída (downstream) enviá-los.

Isso permite o Oversubscription (sobreassinatura). Você pode pegar um slot x8 da CPU (largura de banda de entrada) e conectar 16 SSDs NVMe nele através do switch. Obviamente, se todos os SSDs escreverem ao mesmo tempo, haverá um gargalo no link x8, mas você ganha conectividade massiva.

Figura: O cérebro da operação: um chip switch PCIe gerenciando o tráfego de dados.

Figura: O cérebro da operação: um chip switch PCIe gerenciando o tráfego de dados.

💡 Dica Pro: Em storages de "Cold Data" ou backup, o oversubscription é excelente. Você raramente acessará todos os discos na velocidade máxima simultaneamente, então economizar pistas da CPU usando um switch é uma estratégia inteligente de arquitetura.

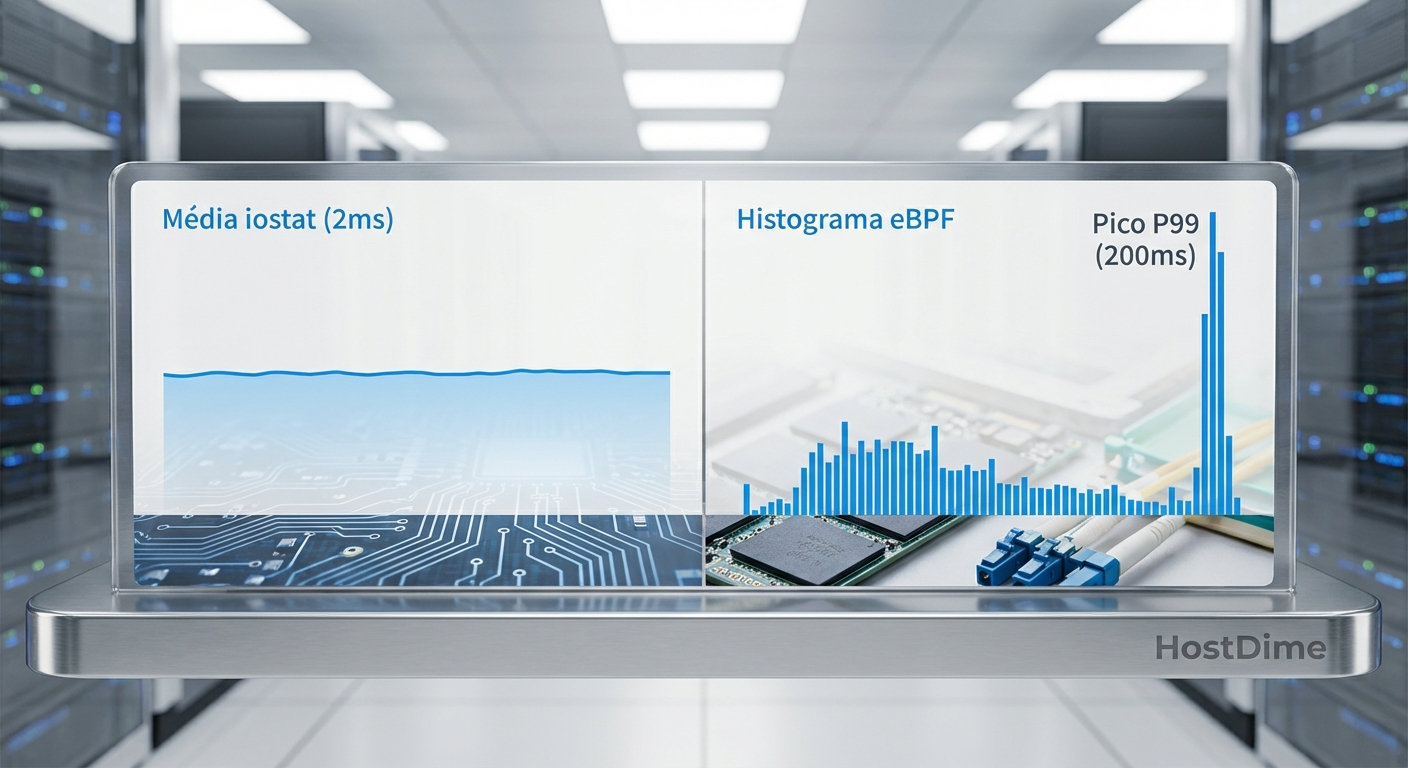

Latência: quando nanossegundos custam milhões

Aqui entra o debate de performance pura. Em cargas de trabalho de High-Frequency Trading (HFT) ou bancos de dados em memória extremamente sensíveis, cada nanossegundo conta.

Um switch PCIe introduz latência. Ele precisa receber o pacote, ler o cabeçalho, verificar erros e encaminhá-lo. Estamos falando de um acréscimo de 100 a 150 nanossegundos (ns) em switches modernos Gen4 ou Gen5.

Para um usuário doméstico ou mesmo um servidor de arquivos convencional, 150ns é imperceptível. Mas em um cluster de computação onde a latência de acesso à memória é medida, essa "pedágio" do switch pode ser inaceitável. A bifurcação, sendo passiva, opera na "velocidade do fio" (wire speed).

O pesadelo do Hot-Swap e isolamento de falhas

Se a bifurcação ganha em velocidade, ela perde feio em segurança. Este é o ponto crítico para ambientes Enterprise.

Imagine que um SSD NVMe falhe catastroficamente, enviando sinais erráticos (garbage data) para o barramento, ou cause um curto-circuito nos pinos de dados.

Na Bifurcação: Esse ruído vai direto para o Root Complex da CPU. O resultado frequente é um erro fatal de sistema (Machine Check Exception), tela azul ou reinicialização espontânea do servidor.

No Switch PCIe: O switch atua como um firewall elétrico. Ele possui recursos como DPC (Downstream Port Containment). Se um SSD enlouquecer, o switch detecta o erro, corta a comunicação daquela porta específica e avisa a CPU: "O drive na porta 3 morreu, mas o resto está seguro". O servidor continua rodando.

Figura: O recurso DPC (Downstream Port Containment) em ação: isolando um drive defeituoso para salvar o servidor.

Figura: O recurso DPC (Downstream Port Containment) em ação: isolando um drive defeituoso para salvar o servidor.

Além disso, o Hot-Swap (troca a quente) em bifurcação é uma roleta russa. Embora a especificação PCIe suporte "surprise removal", muitas BIOS de placas-mãe consumer ou workstation não lidam bem com a remoção súbita de 4 pistas PCIe diretas da CPU. Switches PCIe são projetados especificamente para gerenciar a conexão e desconexão elétrica suave dos drives.

Tabela Comparativa: Bifurcação vs Switch PCIe

| Característica | Bifurcação PCIe (Passiva) | Switch PCIe (Ativa) |

|---|---|---|

| Custo de Implementação | Baixo (Requer apenas trilhas/cabos) | Alto (Chips custam $50-$200+) |

| Latência Adicional | Zero (Wire speed) | ~100-150ns |

| Escalabilidade | Limitada às pistas da CPU (1:1) | Alta (Oversubscription possível) |

| Consumo de Energia | Insignificante | 5W a 15W por chip switch |

| Segurança (Hot-Swap) | Risco de instabilidade/Crash | Robusto (Isolamento de porta) |

| Compatibilidade | Depende estritamente da BIOS/Mobo | Universal (Transparente ao host) |

Compatibilidade e o ecossistema atual

É vital notar que a bifurcação está se tornando mais comum, mas ainda é uma barreira. Placas-mãe HEDT (Threadripper, Xeon-W) geralmente suportam. Placas consumer (Z790, X670) têm suporte limitado, muitas vezes apenas no slot principal da GPU.

Já os switches PCIe são agnósticos. Você pode pegar uma placa HBA (Host Bus Adapter) baseada em switch ou uma placa riser com chip PLX e colocá-la em um sistema antigo que não sabe o que é bifurcação, e ela funcionará. O switch apresenta um único dispositivo à CPU e gerencia os SSDs internamente.

⚠️ Perigo: Cuidado com adaptadores baratos "M.2 x4 para PCIe x16" vendidos em marketplaces. Se eles não tiverem um chip switch visível e sua placa-mãe não suportar bifurcação x4x4x4x4, você verá apenas um SSD. Não existe mágica: ou a CPU divide, ou um chip divide.

Figura: A diferença física: adaptador passivo (bifurcação) vs. ativo (switch).

Figura: A diferença física: adaptador passivo (bifurcação) vs. ativo (switch).

Veredito: velocidade bruta ou blindagem?

A escolha entre switch e bifurcação define a personalidade do seu storage.

Se você está construindo uma workstation de edição de vídeo, um laboratório doméstico ou um sistema de trading, a bifurcação é a vencedora. Ela entrega a performance nativa do NVMe sem custos extras, desde que você valide a compatibilidade da sua placa-mãe.

Por outro lado, se você gerencia um Datacenter, um provedor de Cloud ou um Storage SAN onde o SLA é sagrado, o switch PCIe é obrigatório. A capacidade de isolar um drive defeituoso sem derrubar o sistema e a flexibilidade de conectar dezenas de drives compensam largamente o custo e a latência marginal. Em infraestrutura crítica, a previsibilidade supera a velocidade bruta.

Perguntas Frequentes (FAQ)

A bifurcação PCIe reduz a velocidade do SSD NVMe?

Não. A bifurcação apenas divide as pistas (lanes) existentes da CPU (ex: x16 para x4x4x4x4) sem intermediários, mantendo a velocidade nativa e a menor latência possível. É uma conexão elétrica direta.Por que usar um switch PCIe se ele adiciona latência?

Switches PCIe (como chips Broadcom/PLX) permitem conectar mais drives do que a CPU suporta nativamente (oversubscription) e oferecem recursos vitais para enterprise, como isolamento de erros e hot-swap seguro, que a bifurcação muitas vezes não gerencia bem. A latência adicionada (~150ns) é um preço pequeno pela estabilidade em servidores.Qualquer placa-mãe suporta bifurcação PCIe?

Não. O suporte à bifurcação depende estritamente do chipset e da BIOS da placa-mãe. Servidores enterprise geralmente suportam, mas em plataformas consumer ou workstations antigas, o recurso pode estar ausente ou limitado apenas ao slot principal da GPU.

André Linhares

Engenheiro de Performance (Kernel/IO)

"Vivo no kernel space caçando latência com eBPF. Para mim, context switches excessivos são inimigos pessoais e cada ciclo de CPU desperdiçado é uma ofensa técnica."